Abderazek Ben Abdallah

# Advanced Multicore Systems-On-Chip

Architecture, On-Chip Network, Design

## Advanced Multicore Systems-On-Chip

#### Abderazek Ben Abdallah

# Advanced Multicore Systems-On-Chip

Architecture, On-Chip Network, Design

Abderazek Ben Abdallah School of Computer Science and Engineering The University of Aizu Aizu-Wakamatsu, Fukushima Japan

ISBN 978-981-10-6091-5 ISBN 978-981-10-6092-2 (eBook) DOI 10.1007/978-981-10-6092-2

Library of Congress Control Number: 2017948616

#### © Springer Nature Singapore Pte Ltd. 2017

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature

The registered company is Springer Nature Singapore Pte Ltd.

The registered company address is: 152 Beach Road, #21-01/04 Gateway East, Singapore 189721, Singapore

#### **Preface**

Nowadays, the technology has become an essential pawn in our life that is not restricted anymore to academic research or critical missions; but it is moving away to provide the simplest and easiest services that we need or desire for our daily life. With the expanse of technology and the rising of new trends every day, the necessity to process information anywhere and anytime is becoming the main goal of developers and manufacturers.

Systems on chip (SoCs) are embedded systems composed of several modules (processors, memories, input/output peripherals, etc.) on a single chip. With SoCs, it is now possible to process information and execute critical tasks at higher speed and lower power on a tiny chip. This is due to the increasing number of transistors that can be embedded on a single chip, which keeps doubling approximately every 2 years as Intel co-founder Gordon Moore predicted in 1965. This made shrinking the chip size while maintaining high performance possible. This technology scaling has allowed SoCs to grow continuously in component count and complexity and evolve to systems with many processors embedded on a single SoC. With such high integration level available, the development of multi and many cores on a single die has become possible.

Historically, the SoCs paradigm has evolved from fairly simple unicore single memory designs to complex homogeneous/heterogeneous multicore SoC (MCSoC) systems consisting of a large number of intellectual property (IP) cores on the same silicon. To meet the challenges arising from high computational demands posed by latest state-of-the-art embedded and consumer electronic devices, most current systems are based on such paradigm, which represents a real revolution in many aspects of computing.

The attraction of multicore processing for power reduction is compelling in embedded and in general purpose computing. By splitting a set of tasks among multiple cores, the operating frequency necessary for each core can be reduced, thereby facilitating a reduction in the voltage on each core. As dynamic power is proportional to the frequency and to the square of the voltage, we are able to obtain a sizable gain, even though we may have more cores running.

viii Preface

As more and more cores are integrated into these designs to share the ever increasing processing load, the primary challenges are geared toward efficient memory hierarchy, scalable system interconnect, new programming models, and efficient integration methodology for connecting such heterogeneous cores into a single system capable of leveraging their individual flexibility.

Current design methods are inclined toward mixed hardware/software (HW/SW) co-designs, targeting multicore SoCs for application specific domains. To decide on the lowest cost mix of cores, designers must iteratively map the device's functionality to a particular HW/SW partition and target architectures. In addition, to connect the heterogeneous cores, the architecture requires high performance-based complex communication architectures and efficient communication protocols, such as hierarchical bus, point-to-point connection, or the recent new interconnection paradigm—network on chip.

Software development also becomes far more complex due to the difficulties in breaking a single processing task into multiple parts that could be processed separately and then reassembled later. This reflects the fact that certain processor jobs could not possibly be easily parallelized to run concurrently on multiple processing cores and that load balancing between processing cores—especially heterogeneous cores—is extremely difficult.

This book is organized into nine chapters. The book stands independent and we have made every attempt to make each chapter self-contained as well.

Chapter 1 introduces multicore systems on chip (MCSoCs) architectures and explores SoCs technology and the challenges it presents to organizations and developers building next-generation multicore SoCs-based systems.

Understanding the technological landscape and design methods in some level of details are very important. This is because so many design decisions in multicore architecture today are guided by the impact of the technology. Chapter 2 presents design challenges and conventional design methods of MCSoCs. It also describes a so-called scalable core-based method for systematic design environment of application specific heterogeneous multicore SoC architectures. The architecture design used in conventional methods of multicore SoCs and custom multiprocessor architectures are not flexible enough to meet the requirements of different application domains and not scalable enough to meet different computation needs and different complexities of various applications. Therefore, designers should be aware of existing design methods and also be ready to innovate or adapt appropriate design methods for individual target platform.

Understanding the software and hardware building blocks and the computation power of individual components in these complex MCSoCs is necessary for designing power-, performance-, and cost-efficient systems. Chapter 3 describes in details the architectures and functions of the main building blocks that are used to build such complex multicore SoCs. Readers with a relevant background in multicore SoC building blocks could effectively skip some of the materials mentioned in this chapter. The knowledge of these aspects is not an absolute requirement for understanding the rest of the book, but it does help novice students or beginners to

Preface

get a glimpse of the big picture of a heterogeneous or homogeneous MCSoC organization.

Whether homogeneous, heterogeneous, or hybrid multicore SoCs, IP cores must be connected in a high-performance, scalable, and flexible manner. The emerging technology that targets such connections is called an on-chip interconnection network, also known as a network on chip (NoC), and the philosophy behind the emergence of such innovation has been summarized by William Dally at Stanford University as *route packets, not wires*.

Chapters 4–6 presents fundamental and advanced on-chip interconnection network technologies for multi- and many-core SoCs. These three chapters are all very important part of the book since they allow the reader to understand what needed microarchitecture for on-chip routers and network interfaces are essential towards meeting latency, area, and power constraints. Reader will also understand practical issues about what system architecture (topology, routing, flow control, NI, and 3D integration) is most suited for these on-chip networks.

With the rise of multicore and many-core systems, concurrency becomes a major issue in the daily life of a programmer. Thus, compiler and software development tools will be critical towards helping programmers create high-performance software. Programmers should make sure that their parallelized program codes would not cause race condition, memory-access deadlocks, or other faults that may crash their entire systems. Chapter 7 describes a novel parallelizing compiler design for high-performance computing.

Power dissipation continues to be a primary design constraint and concern in single and multicore systems. Increasing power consumption not only results in increasing energy costs, but also results in high die temperatures that affect chip reliability, performance, and packaging cost. Chapter 8 provides a detailed investigation of power reduction techniques for multicore SoC at components and network levels. Energy conservation has been largely considered in the hardware design, in general and also in embedded multicore system's components, such as CPUs, disks, displays, memories, and so on. Significant additional power savings could be also achieved by incorporating low power methods into the design of network protocols used for data communication (audio, video, etc.).

Chapter 9 ties together previous chapters and presents a real embedded multicore SoC system design targeted for elderly health monitoring. For this book, we used our experience to illustrate the complete design flow for a multicore SoC running an electrocardiogram (ECG) application in parallel. Thanks to the recent technological advances in wireless networking, embedded microelectronics, and the Internet, computer and biomedical scientists are now capable to fundamentally modernize and change the way health care services are deployed. Discussions on how to design the algorithms, architecture, register-transfer level implementation, and FPGA prototyping and validation for ECG processing are presented in details.

This book took nearly 2 years to complete. It evolved from our first book and is derived from our teaching experiences in embedded system designs and architecture to both undergraduate and graduate students. Multicore systems paradigm created stupendous opportunities to increase overall system performance, but also created

x Preface

many design challenges that designers must now overcome. Thus we must continue innovating new algorithms and techniques to solve these challenges.

The author is thankful to numerous colleagues and graduate students for their lively discussions and their help in preparing the manuscript of this book. Special thanks are due to the publishers in bringing out this book quickly, yet maintaining very high quality.

Aizu-Wakamatsu, Japan

Abderazek Ben Abdallah

### **Contents**

| 1 | intr | oauctio  | on to Multicore Systems On-Chip       | 1  |

|---|------|----------|---------------------------------------|----|

|   | 1.1  | The M    | Iulticore Revolution                  | 1  |

|   |      | 1.1.1    | The Impact of Moore's Law             | 2  |

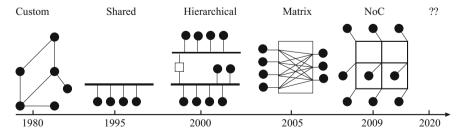

|   |      | 1.1.2    | On-Chip Interconnection Schemes       | 2  |

|   |      | 1.1.3    | Parallelism and Performance           | 4  |

|   |      | 1.1.4    | Parallel Hardware Architectures       | 6  |

|   |      | 1.1.5    | The Need for Multicore Computing      | 8  |

|   |      | 1.1.6    | Multicore SoCs Potential Applications | 8  |

|   | 1.2  | Multic   | core SoC Basics                       | 10 |

|   |      | 1.2.1    | Programmability Support               | 10 |

|   |      | 1.2.2    | Software Organization                 | 11 |

|   |      | 1.2.3    | Programming Multicore Systems         | 12 |

|   |      | 1.2.4    | Multicore Implementations             | 13 |

|   | 1.3  | Multic   | core SoCs Design Challenges           | 15 |

|   |      | 1.3.1    | Cache Coherence                       | 15 |

|   |      | 1.3.2    | Power and Temperature                 | 16 |

|   |      | 1.3.3    | Multi-threading and Memory Management | 16 |

|   |      | 1.3.4    | On-Chip Interconnection Networks      | 17 |

|   |      | 1.3.5    | Reliability Issues                    | 17 |

|   | 1.4  | Chapte   | er Summary                            | 17 |

|   | Refe | erences. |                                       | 18 |

| 2 | Mul  | ticore S | SoCs Design Methods                   | 19 |

|   | 2.1  | Introd   | uction                                | 19 |

|   | 2.2  | Design   | n Space Exploration                   | 20 |

|   | 2.3  |          | el Software Development Phase         | 22 |

|   |      | 2.3.1    |                                       | 22 |

|   |      | 2.3.2    | Language Extensions Schemes           | 23 |

|   |      | 2.3.3    | Language Extensions with APIs         | 24 |

|   |      | 2.3.4    | Model-Based Schemes                   | 24 |

|   |      |          |                                       |    |

xii Contents

|   | 2.4 |       | ic Architecture Template (GAT) for Real Multicore SoC | 25       |

|---|-----|-------|-------------------------------------------------------|----------|

|   |     | _     |                                                       | 25<br>25 |

|   |     | 2.4.1 | $\epsilon$                                            | 25<br>26 |

|   |     | 2.4.2 | $\mathcal{E}$                                         | 26       |

|   |     | 2.4.3 |                                                       | 28       |

|   | 2.5 | 2.4.4 | <b>5</b>                                              | 33<br>35 |

|   | 2.5 |       | <b>5</b>                                              | 35<br>35 |

|   |     |       |                                                       |          |

| 3 |     |       | 8                                                     | 39<br>20 |

|   | 3.1 |       |                                                       | 39       |

|   |     | 3.1.1 | $\varepsilon$                                         | 41       |

|   |     | 3.1.2 | $\epsilon$                                            | 43       |

|   |     | 3.1.3 | r r                                                   | 44       |

|   | 2.2 | 3.1.4 | 11 6                                                  | 45       |

|   | 3.2 |       | $\mathcal{E}$                                         | 46       |

|   |     | 3.2.1 |                                                       | 48       |

|   |     | 3.2.2 | · · · · · · · · · · · · · · · · · · ·                 | 48       |

|   |     | 3.2.3 |                                                       | 50<br>50 |

|   |     | 3.2.4 |                                                       | 50<br>52 |

|   |     | 3.2.5 | 1 2 1                                                 | 52<br>52 |

|   |     | 3.2.6 | 1                                                     | 53<br>54 |

|   | 2.2 | 3.2.7 |                                                       | 54<br>56 |

|   | 3.3 | 3.3.1 |                                                       | 30<br>56 |

|   |     | 3.3.2 | 71 1 7                                                | 50<br>58 |

|   |     | 3.3.3 | 1                                                     | 30<br>58 |

|   |     | 3.3.4 | 1 2                                                   | 50<br>59 |

|   | 3.4 |       | Ş                                                     | 59<br>61 |

|   | 3.4 | 3.4.1 |                                                       | 61       |

|   |     | 3.4.1 |                                                       | 63       |

|   | 3.5 |       |                                                       | 65       |

|   |     | -     | <b>5</b>                                              | 65       |

|   |     |       |                                                       |          |

| 4 |     |       |                                                       | 67       |

|   | 4.1 |       |                                                       | 67       |

|   | 4.2 |       | 1                                                     | 69<br>60 |

|   |     | 4.2.1 | 1 23                                                  | 69<br>54 |

|   |     |       | •                                                     | 71       |

|   |     | 4.2.3 |                                                       | 74       |

|   |     | 4.2.4 | 2 2                                                   | 76       |

|   | 4.3 |       |                                                       | 82       |

|   |     | 4.3.1 |                                                       | 82       |

|   |     | 4.3.2 | 1 6                                                   | 84       |

|   |     | 4.3.3 | Crossbar Design                                       | 88       |

Contents xiii

|   |                     | 4.3.4    | Limitations of Regular Mesh Topology                  |     |

|---|---------------------|----------|-------------------------------------------------------|-----|

|   |                     | 4.3.5    | SPL Insertion Algorithm                               | 90  |

|   |                     | 4.3.6    | Network Interface Design                              | 94  |

|   | 4.4                 | Chapt    | er Summary                                            | 105 |

|   | Refe                | erences. |                                                       | 105 |

| 5 | Adv                 | anced    | Multicore SoC Interconnects                           | 107 |

|   | 5.1                 |          | uction                                                |     |

|   | 5.2                 |          | -Dimensional On-Chip Interconnect                     |     |

|   | 3.2                 | 5.2.1    | 3D-NoC Versus 2D-NoC                                  |     |

|   |                     | 5.2.2    | Routing Algorithms                                    |     |

|   |                     | 5.2.3    | Topology Design.                                      |     |

|   |                     | 5.2.4    | Switching Policy                                      |     |

|   |                     | 5.2.5    | 3D-NoC Router Architecture Design                     |     |

|   |                     | 5.2.6    | Network Interface Architecture                        |     |

|   |                     | 5.2.7    | 3D-NoC Design Evaluation.                             |     |

|   |                     | 5.2.8    | Conclusion                                            |     |

|   | 5.3                 |          | nic On-Chip Interconnect for High-Bandwidth Multicore | 1.0 |

|   |                     |          | ·····                                                 | 143 |

|   |                     | 5.3.1    | Photonic Communication Building Blocks                |     |

|   |                     | 5.3.2    | Design Challenges                                     |     |

|   |                     | 5.3.3    | Fault Models                                          |     |

|   |                     | 5.3.4    | Fault-Tolerant Photonic Network-on-Chip Architecture  |     |

|   |                     | 5.3.5    | Evaluation                                            | 160 |

|   |                     | 5.3.6    | Related Literature                                    |     |

|   |                     | 5.3.7    | Chapter Summary                                       |     |

|   | Refe                | erences. |                                                       |     |

| , |                     |          |                                                       |     |

| 6 | <b>3</b> D .<br>6.1 |          | tion Technology for Multicore Systems On-Chip         |     |

|   | 6.2                 |          | tegration Technology                                  |     |

|   | 0.2                 |          | Tolerant TSV Cluster for 3D Integration               |     |

|   | 6.3                 | 6.2.1    |                                                       |     |

|   | 0.3                 | 6.3.1    | ive Online TSV Sharing Algorithm                      |     |

|   |                     | 6.3.2    | TSV-Clusters Return                                   |     |

|   |                     | 6.3.3    | Weight Adjustment                                     |     |

|   |                     | 6.3.4    | Design Optimization                                   |     |

|   | 6.4                 |          | ation Results                                         |     |

|   | 0.4                 | 6.4.1    |                                                       | 190 |

|   |                     | 6.4.2    | Performance Evaluation.                               | 190 |

|   |                     | 6.4.3    | Latency Evaluation                                    |     |

|   |                     | 6.4.4    | Throughput Evaluation                                 |     |

|   |                     | 6.4.5    | Router Hardware Complexity                            |     |

|   |                     | 6.4.6    | Comparison                                            |     |

|   | 6.5                 |          | er Summary                                            |     |

|   |                     |          | er Summary                                            | 197 |

|   | Neit                | achees.  |                                                       | 19/ |

xiv Contents

| 7 | Para | allelizin | g Compiler for Single and Multicore Computing      | 201 |

|---|------|-----------|----------------------------------------------------|-----|

|   | 7.1  | Introd    | uction                                             | 201 |

|   |      | 7.1.1     | Instruction Level Parallelism                      | 202 |

|   |      | 7.1.2     | Queue Computation Model                            | 204 |

|   | 7.2  | Paralle   | el Queue Compiler                                  | 204 |

|   |      | 7.2.1     | Queue Processor Overview                           | 204 |

|   |      | 7.2.2     | Compiling for One-Offset QueueCore Instruction Set | 205 |

|   | 7.3  | Paralle   | elizing Compiler Framework                         | 208 |

|   |      | 7.3.1     | One-Offset P-Code Generation Phase                 | 209 |

|   |      | 7.3.2     | Offset Calculation Phase                           | 212 |

|   |      | 7.3.3     | Instruction Scheduling Phase                       | 213 |

|   |      | 7.3.4     | Natural Instruction Level Parallelism Extraction:  |     |

|   |      |           | Statement Merging Transformation                   | 214 |

|   |      | 7.3.5     | Assembly Generation Phase                          | 216 |

|   | 7.4  | Paralle   | elizing Compiler Development Results               | 217 |

|   |      | 7.4.1     | Queue Compiler Evaluation                          | 218 |

|   |      | 7.4.2     | Comparison of Generated QueueCore Code             |     |

|   |      |           | with Optimized RISC Code                           | 220 |

|   | 7.5  | Chapte    | er Summary                                         | 221 |

|   | Refe | erences.  |                                                    | 222 |

| 8 | Pow  | er Opt    | imization Techniques for Multicore SoCs            | 225 |

|   | 8.1  |           | uction                                             | 225 |

|   | 8.2  | Power     | -Aware Technological-Level Design Optimizations    | 227 |

|   |      | 8.2.1     | Factors Affecting CMOS Power Consumption           | 227 |

|   |      | 8.2.2     | Reducing Voltage and Frequency                     | 228 |

|   |      | 8.2.3     | Reducing Capacitance                               | 229 |

|   | 8.3  | Power     | -Aware Logic-Level Design Optimizations            | 230 |

|   |      | 8.3.1     | Clock Gating                                       | 230 |

|   |      | 8.3.2     | Logic Encoding                                     | 231 |

|   |      | 8.3.3     | Data Guarding                                      | 232 |

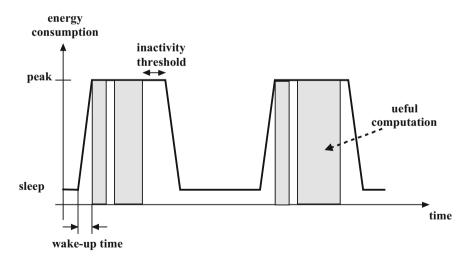

|   | 8.4  | Power     | -Aware System Level Design Optimizations           | 232 |

|   |      | 8.4.1     | Hardware System Architecture Power Consumption     |     |

|   |      |           | Optimizations                                      | 233 |

|   |      | 8.4.2     | Operating System Power Consumption Optimization    | 236 |

|   |      | 8.4.3     | Application, Compilation Techniques, and Algorithm | 238 |

|   |      | 8.4.4     | Energy Reduction in Network Protocols              | 238 |

|   | 8.5  | Chapte    | er Summary                                         | 242 |

|   | Refe | erences.  |                                                    | 242 |

| 9 | Rea  | l Deign   | of Embedded Multicore SoC for Health Monitoring    | 245 |

|   | 9.1  |           | uction                                             | 245 |

|   |      |           | Flectrocardiography and Heart Diseases             | 246 |

Contents xv

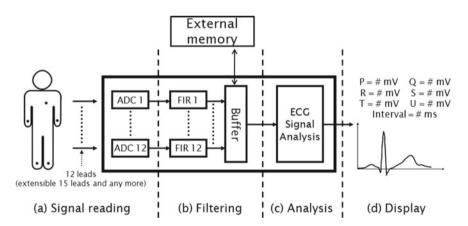

|    | 9.2   | Applic  | cation Specific Digital Signal Processing | 248  |

|----|-------|---------|-------------------------------------------|------|

|    |       | 9.2.1   | Analog and Digital Signals                | 250  |

|    |       | 9.2.2   | Signal Processing                         | 250  |

|    |       | 9.2.3   | Analog to Digital Conversion              | 250  |

|    | 9.3   | Period  | -Peak ECG Detection Algorithm             | 251  |

|    |       | 9.3.1   | Period Detection                          | 253  |

|    |       | 9.3.2   | Peaks Detection                           | 254  |

|    | 9.4   | Multic  | core SoC Hardware Design                  | 257  |

|    |       | 9.4.1   | Signal Reading                            | 257  |

|    |       | 9.4.2   | Filtering                                 | 258  |

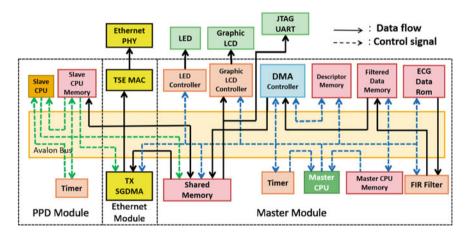

|    |       | 9.4.3   | Data Processing                           | 259  |

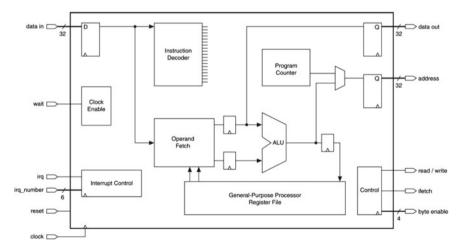

|    |       | 9.4.4   | Processor Core                            | 260  |

|    | 9.5   | Real-T  | Time Monitoring Interface Design          | 261  |

|    |       | 9.5.1   | Data Capturing                            | 261  |

|    |       | 9.5.2   | Data Display and Analysis                 | 262  |

|    | 9.6   | System  | n Hardware and Software Design Evaluation | 265  |

|    |       | 9.6.1   | Hardware Complexity                       | 265  |

|    |       | 9.6.2   | Performance Evaluation                    | 266  |

|    | 9.7   | Chapte  | er Summary                                | 266  |

|    | Refe  | rences. |                                           | 267  |

| In | dex   |         |                                           | 269  |

|    | uca . |         |                                           | /117 |

# **List of Figures**

| Fig. I.I  | Scaling of transistor counts and operating frequency in ICs.   |    |

|-----------|----------------------------------------------------------------|----|

|           | The feature size and design abstraction are also shown         |    |

|           | in the graph                                                   | 3  |

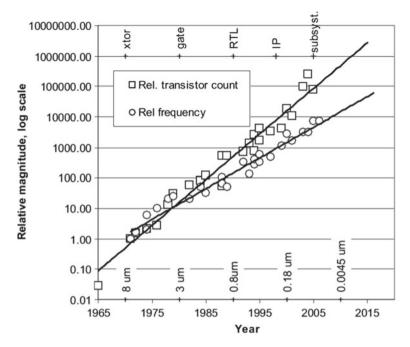

| Fig. 1.2  | Different ways for exploiting parallelism over various system  |    |

|           | organization: a Single core, b Multicore with separate caches, |    |

|           | c Multicore with shared cache, d Multicore with simultaneous   |    |

|           | threading, e Multiprocessor                                    | 6  |

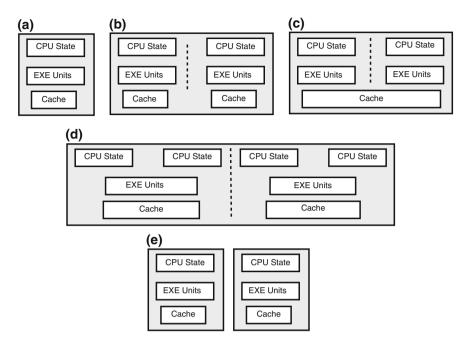

| Fig. 1.3  | From PCB to MCSoC                                              | 7  |

| Fig. 1.4  | Multicore SoC potential applications                           | 9  |

| Fig. 1.5  | Typical multicore SoC architectural view                       | 10 |

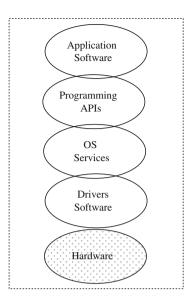

| Fig. 1.6  | Software layers on <i>top</i> of the hardware                  | 12 |

| Fig. 1.7  | Sample OpenMP code using section and parallel directives:      |    |

|           | a Functional decomposition, b Data decomposition               | 13 |

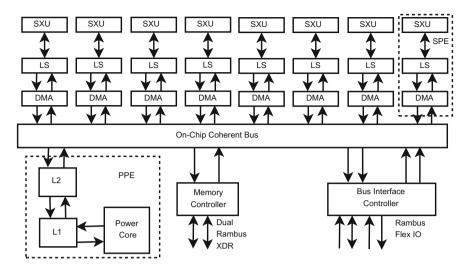

| Fig. 1.8  | Heterogeneous Multicore CELL Organization                      | 14 |

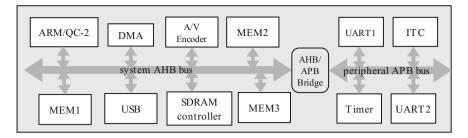

| Fig. 2.1  | SoC typical architecture                                       | 21 |

| Fig. 2.2  | Compiler-based scheme                                          | 22 |

| Fig. 2.3  | Parallel for loop with OpenMP                                  | 24 |

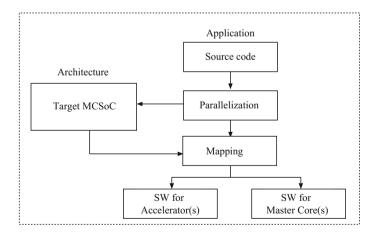

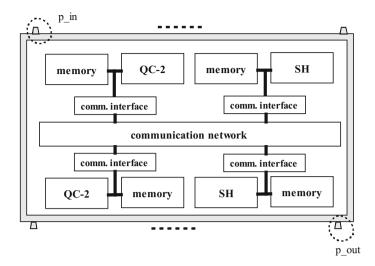

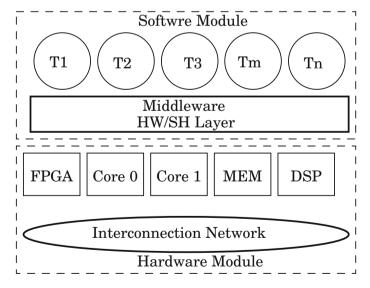

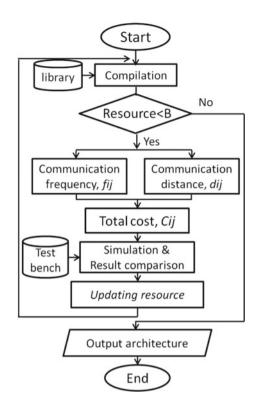

| Fig. 2.4  | Multicore SoC system platform. This is a typical instance      |    |

|           | of the architecture, where the addition of a new core will not |    |

|           | change the principle of the methodology                        | 26 |

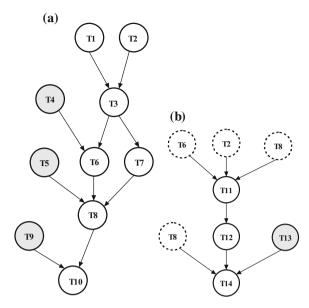

| Fig. 2.5  | Linked task design flow graph (DFG). a Hardware related        |    |

|           | tasks, <b>b</b> Application related tasks                      | 27 |

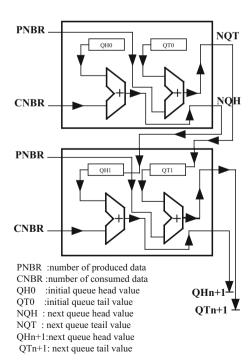

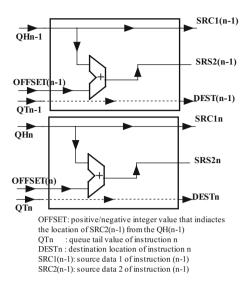

| Fig. 2.6  | Next QH and QT pointers calculation mechanism                  | 29 |

| Fig. 2.7  | QC-2's source 2 address calculation                            | 30 |

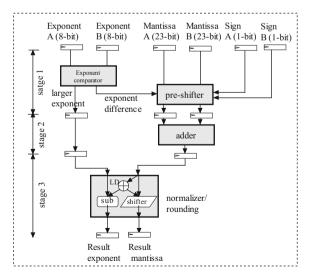

| Fig. 2.8  | QC-2's FADD hardware                                           | 31 |

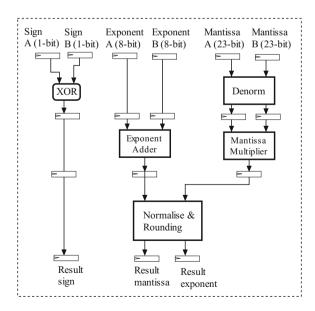

| Fig. 2.9  | QC-2's FMUL hardware                                           | 32 |

| Fig. 2.10 | Resource usage and timing for 256*33 bit QREG unit for         |    |

|           | different coding and optimization strategies                   | 33 |

xviii List of Figures

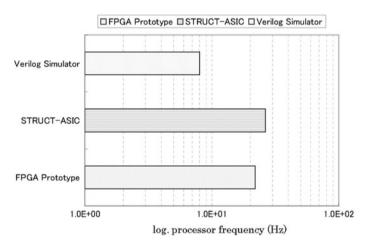

| Fig. 2.11 | hardware implementations of the QC-2 processor. Simulation               |

|-----------|--------------------------------------------------------------------------|

|           | speeds have been converted to a nominal frequency rating to              |

|           | facilitate comparison                                                    |

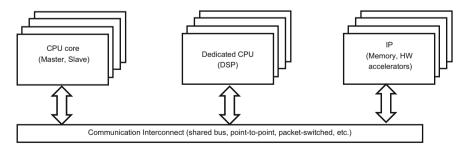

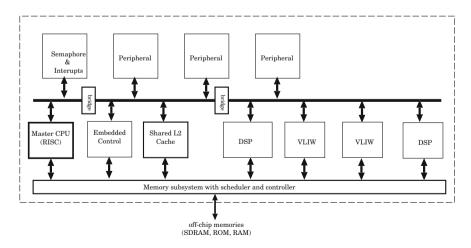

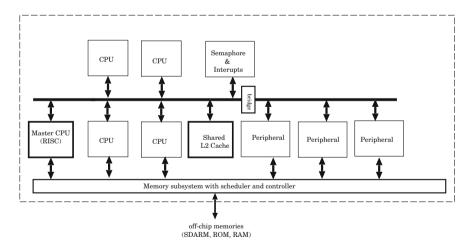

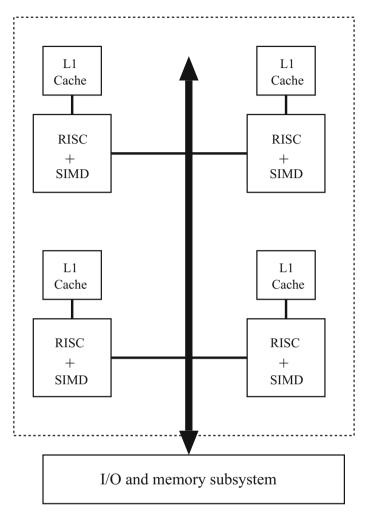

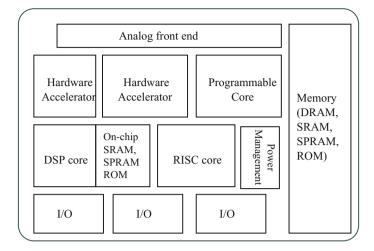

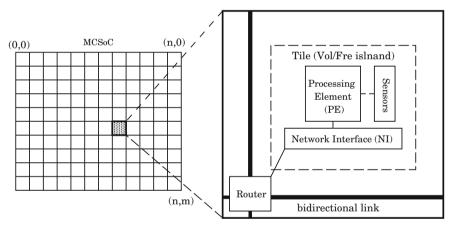

| Fig. 3.1  | General organization view of a modern typical MCSoC                      |

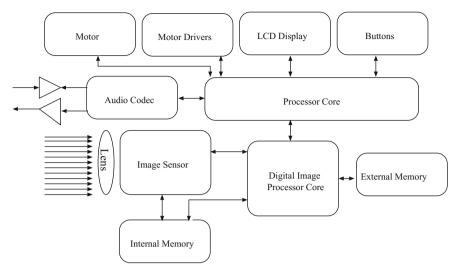

| Fig. 3.2  | Example of an embedded multicore system for a typical digital            |

| 8         | still camera                                                             |

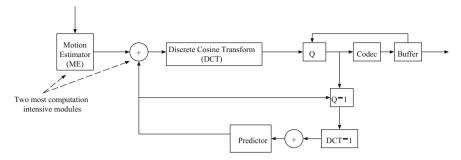

| Fig. 3.3  | Example of MPEG-2 encoder for a heterogeneous                            |

| C         | MCSoC system                                                             |

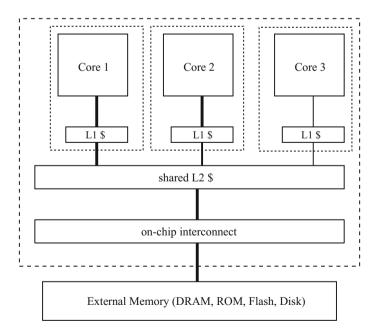

| Fig. 3.4  | Heterogeneous MCSoC organization example                                 |

| Fig. 3.5  | Homogeneous MCSoC organization example                                   |

| Fig. 3.6  | Example of MCSoC application in wireless communication:                  |

| C         | Lucent Daytona MCSoC                                                     |

| Fig. 3.7  | Simplified view of a typical MCSoC architecture with different           |

| C         | core and memory types                                                    |

| Fig. 3.8  | State-of-the-art MCSoC architecture based on network-on-chip             |

| C         | paradigm                                                                 |

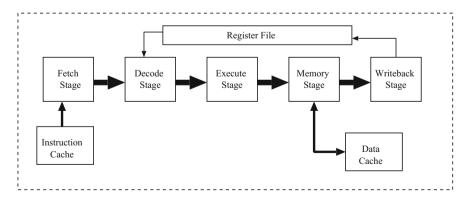

| Fig. 3.9  | Typical 5 pipeline stages of a RISC processor core                       |

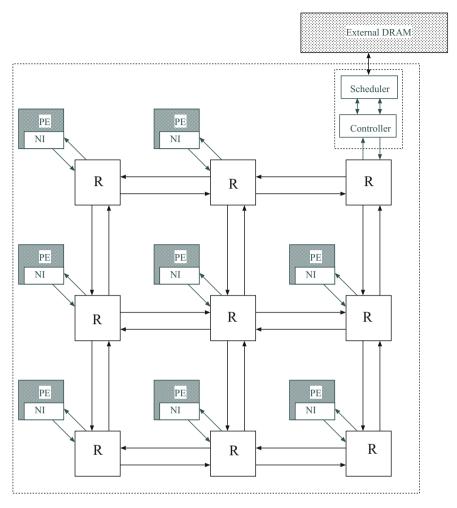

| Fig. 3.10 | Example of MCSoC with single external DRAM memory                        |

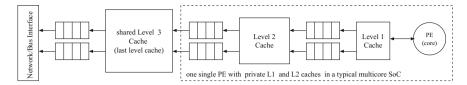

| Fig. 3.11 | Cache organization in a single node of a typical MCSoC                   |

| Fig. 3.12 | Evolution of on-chip communication interconnect                          |

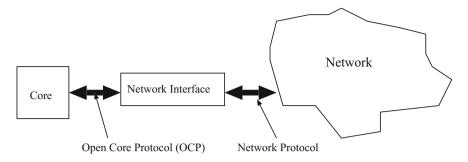

| Fig. 3.13 | Open core protocol (OCP) and Network protocol (NP)                       |

|           | interfacing                                                              |

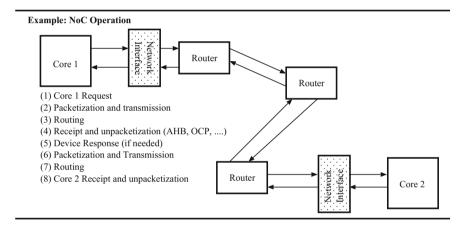

| Fig. 3.14 | NoC operation                                                            |

| Fig. 3.15 | Intellectual property example                                            |

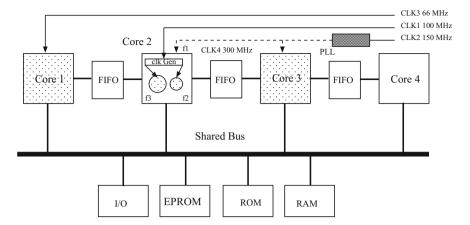

| Fig. 3.16 | Three clock domains MCSoC                                                |

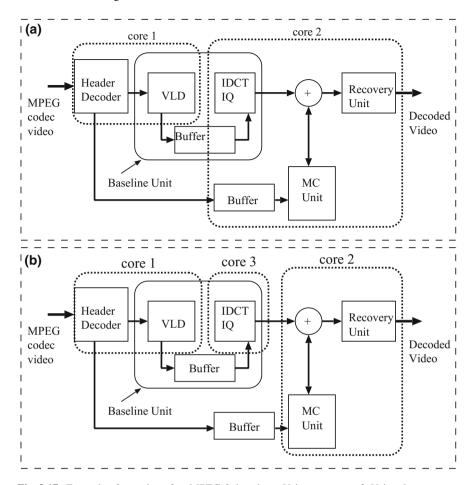

| Fig. 3.17 | Example of mapping of an MPEG-2 decoder. a Using two                     |

| _         | cores, <b>b</b> Using three cores                                        |

| Fig. 3.18 | Simplified view of a MCSoC architecture having different                 |

|           | memories                                                                 |

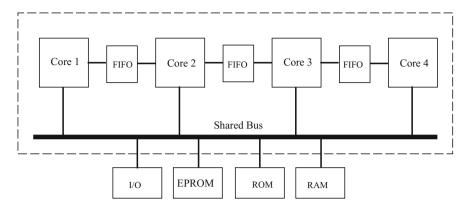

| Fig. 3.19 | Example of four cores communicating via FIFOs                            |

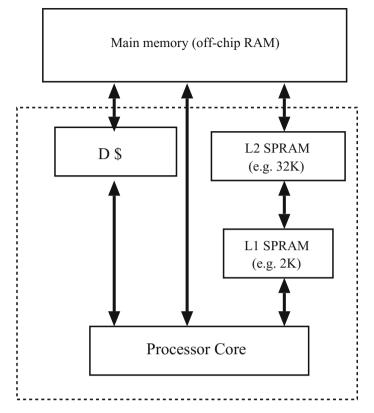

| Fig. 3.20 | MCSoC memory subsystem with SPARM (only                                  |

|           | interconnection for one node is shown for simplicity)                    |

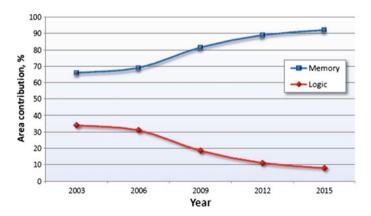

| Fig. 3.21 | Projection of memory/logic composition of power-constrained              |

|           | SoC chips [11]                                                           |

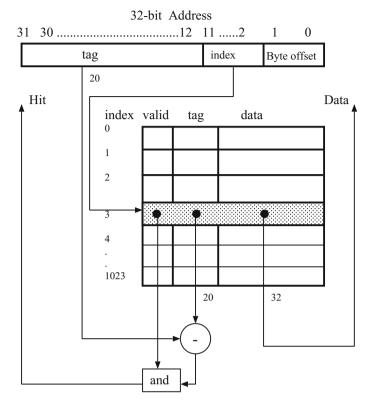

| Fig. 3.22 | Direct-mapped cache organization                                         |

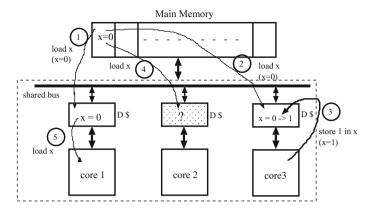

| Fig. 3.23 | Cache coherence problem example without coherence                        |

|           | protocol                                                                 |

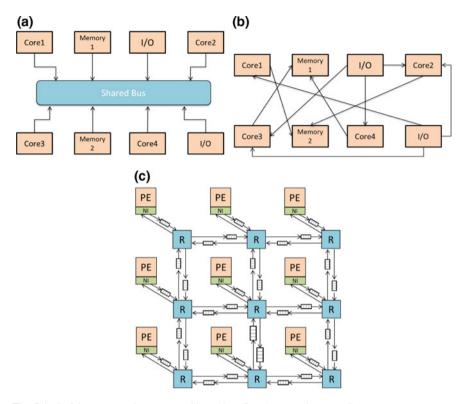

| Fig. 4.1  | Typical paradigms: <b>a</b> circuit switching, <b>b</b> packet switching |

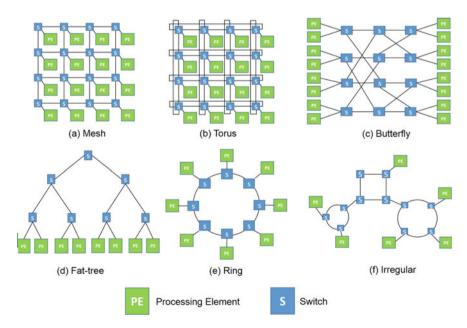

| Fig. 4.2  | Typical NoC topologies                                                   |

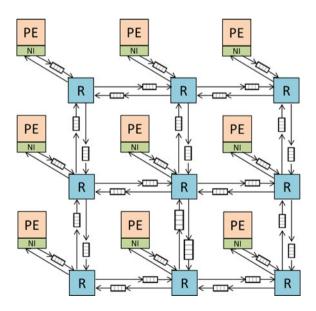

| Fig. 4.3  | Example of a $3 \times 3$ NoC based on mesh topology.                    |

| -         | R: router/switch, PE: processing element,                                |

|           | NI: network interface                                                    |

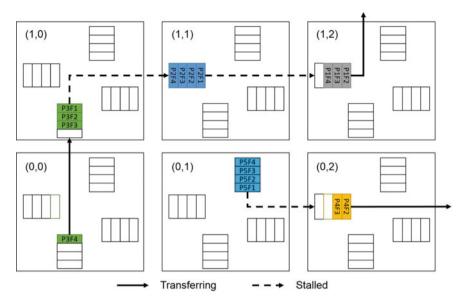

| Fig. 4.4  | Store-and-forward switching                                              |

List of Figures xix

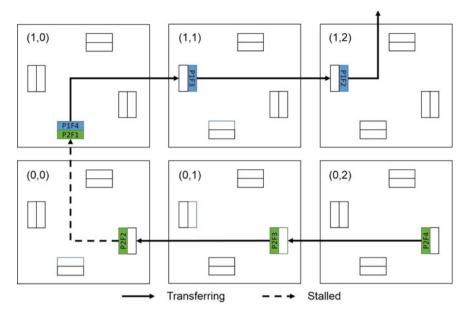

| Fig. 4.5  | Wormhole switching                                                | 73        |

|-----------|-------------------------------------------------------------------|-----------|

| Fig. 4.6  | Virtual-cut-through switching                                     | 74        |

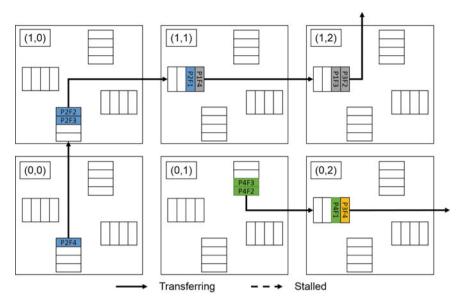

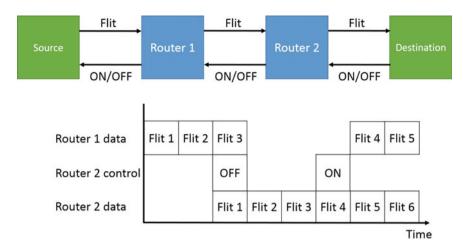

| Fig. 4.7  | ON/OFF flow control                                               | 75        |

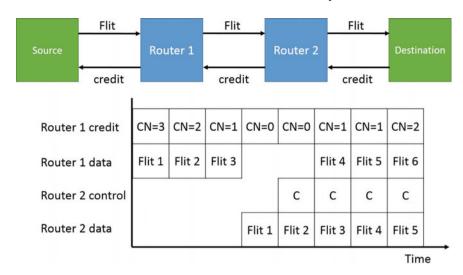

| Fig. 4.8  | Credit-based flow control                                         | 76        |

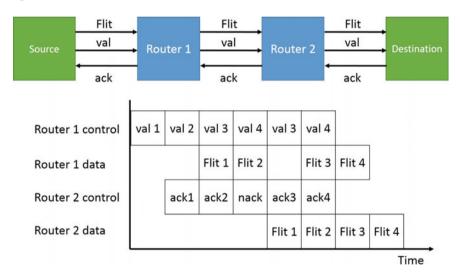

| Fig. 4.9  | ACK/NACK flow control                                             | 76        |

| Fig. 4.10 | Categorization of routing algorithms according to the number      |           |

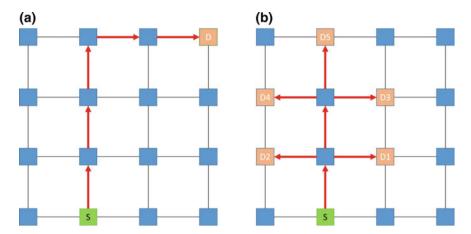

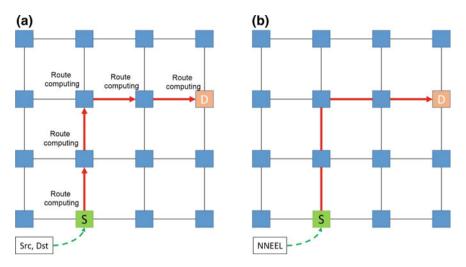

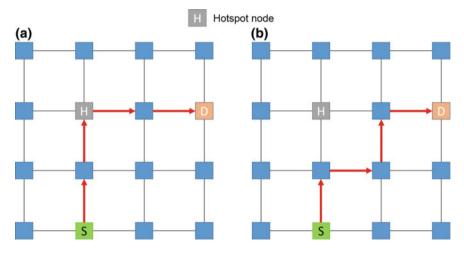

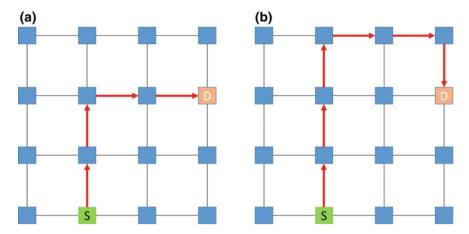

|           | of destinations: a unicast, b multicast                           | 77        |

| Fig. 4.11 | Categorization of routing algorithms according to decision        |           |

|           | locality: <b>a</b> distributed, <b>b</b> source                   | 78        |

| Fig. 4.12 | Categorization of routing algorithms according to adaptivity:     |           |

|           | a deterministic, b adaptive                                       | 78        |

| Fig. 4.13 | Categorization of routing algorithms according to minimality:     |           |

|           | a minimal, b non-minimal                                          | 79        |

| Fig. 4.14 | Deadlock example in adaptive NoC systems                          | 80        |

| Fig. 4.15 | Virtual-channel-based router architecture                         | 80        |

| Fig. 4.16 | Virtual-output-queue-based router architecture                    | 81        |

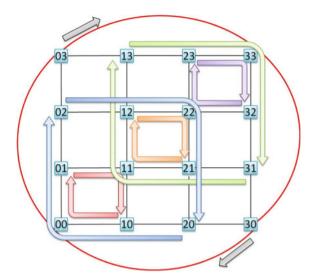

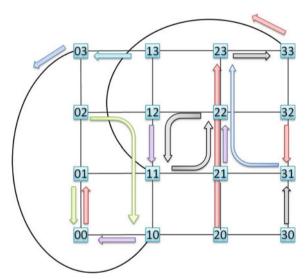

| Fig. 4.17 | $4 \times 4$ mesh topology                                        | 82        |

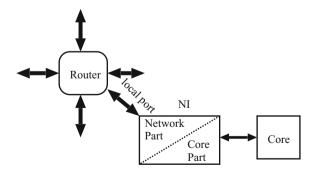

| Fig. 4.18 | External connections to one router                                | 83        |

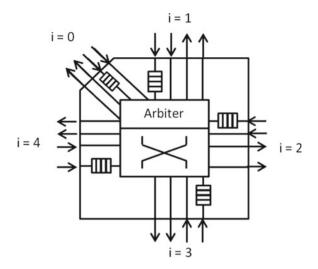

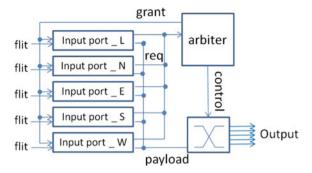

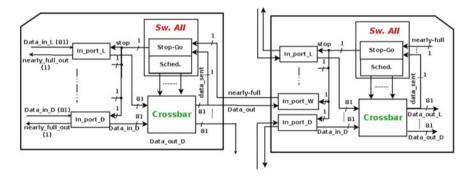

| Fig. 4.19 | ONoC router block diagram                                         | 84        |

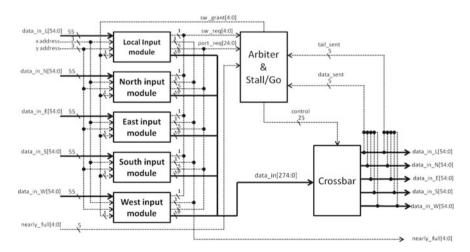

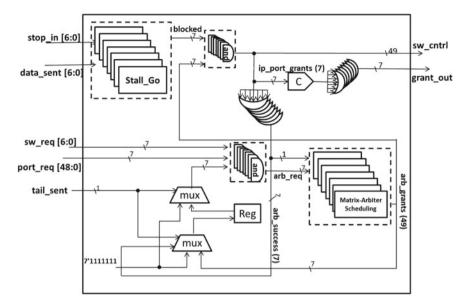

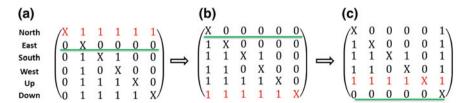

| Fig. 4.20 | Matrix arbitration example                                        | 86        |

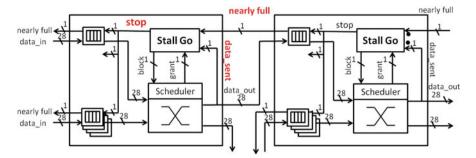

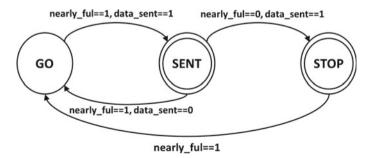

| Fig. 4.21 | Stall-go block diagram                                            | 87        |

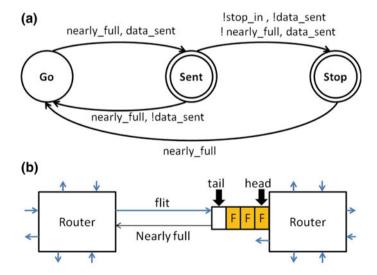

| Fig. 4.22 | <b>a</b> State machine design, <b>b</b> Nearly full signal output | 87        |

| Fig. 4.23 | Arbiter control signals                                           | 88        |

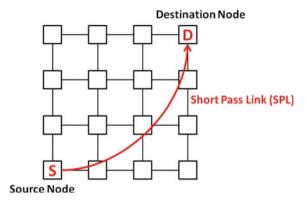

| Fig. 4.24 | Short-path-link (SPL) insertion example                           | 90        |

| Fig. 4.25 | SPL insertion algorithm                                           | 91        |

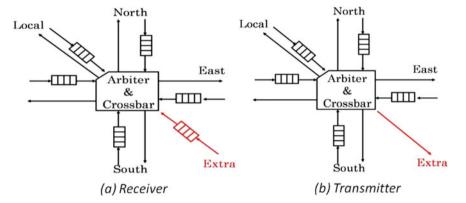

| Fig. 4.26 | Extra-port insertion                                              | 92        |

| Fig. 4.27 | Dimension reversal with 2 SPLs                                    | 93        |

| Fig. 4.28 | Hotspot with 2 SPL                                                | 93        |

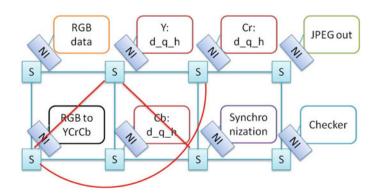

| Fig. 4.29 | JPEG encoder with 3 SPL.                                          | 94        |

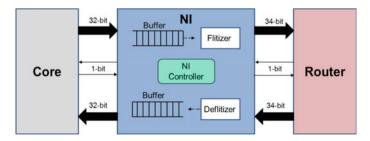

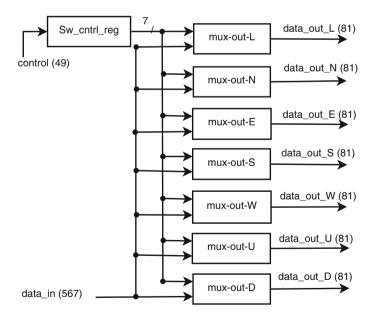

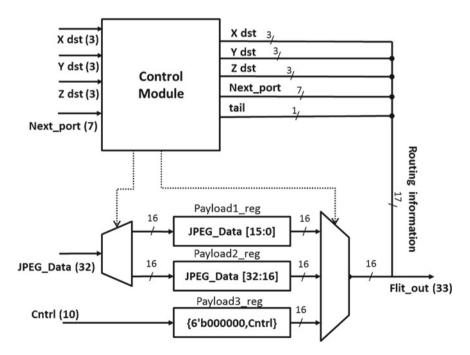

| Fig. 4.30 | Nigh-level view of the network interface                          | 95        |

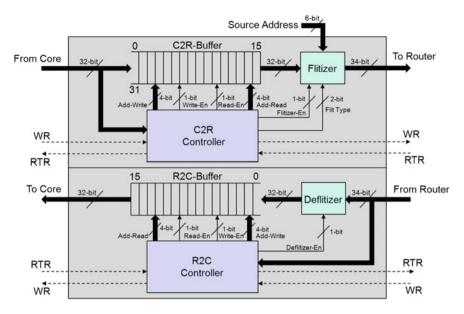

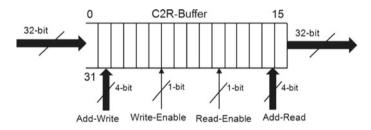

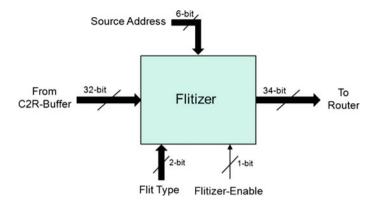

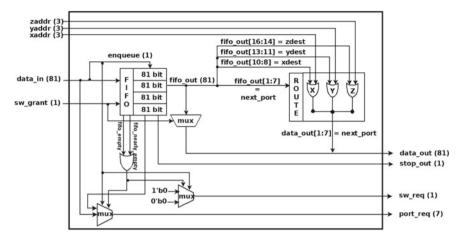

| Fig. 4.31 | Distributed routing NI architecture block diagram                 | 96        |

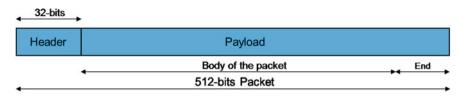

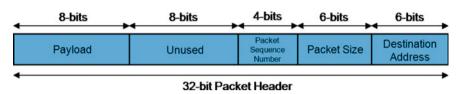

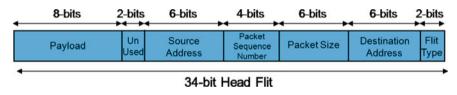

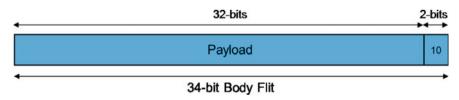

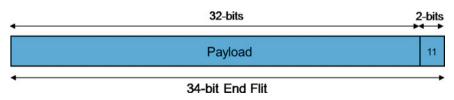

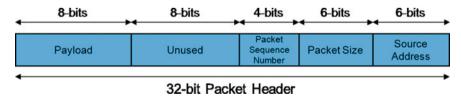

| Fig. 4.32 | Packet format                                                     | 98        |

| Fig. 4.33 | Packet HEADER format                                              | 98        |

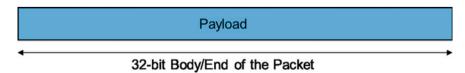

| Fig. 4.34 | BODY and END format                                               | 98        |

| Fig. 4.35 | HEADER flit format                                                | 99        |

| Fig. 4.36 | BODY flit format                                                  | 99        |

| Fig. 4.37 | END flit format.                                                  | 99<br>100 |

| Fig. 4.38 | 1                                                                 | 100       |

| Fig. 4.39 |                                                                   | 100       |

| Fig. 4.40 | $\mathcal{E}$                                                     | 101       |

| Fig. 4.41 |                                                                   | 101       |

| Fig. 4.42 |                                                                   | 102       |

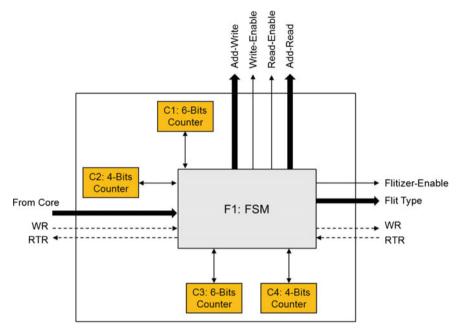

| Fig. 4.43 | Core-to-router (C2R) controller architecture                      | 103       |

xx List of Figures

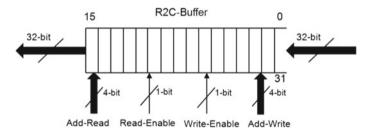

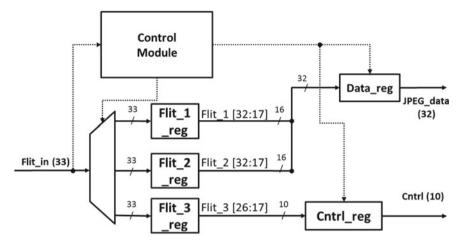

| Fig. 4.44 | Router-to-core (R2C) buffer                                                                | 103 |

|-----------|--------------------------------------------------------------------------------------------|-----|

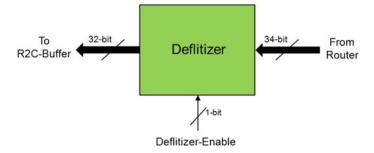

| Fig. 4.45 | Deflitizer module architecture                                                             | 104 |

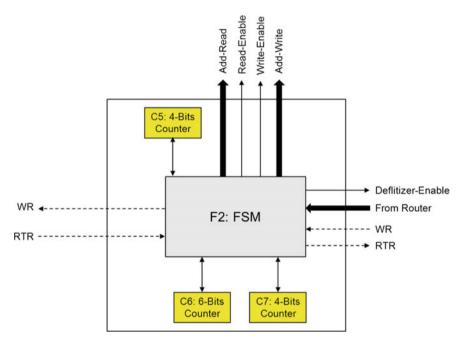

| Fig. 4.46 | R2C controller module architecture                                                         | 104 |

| Fig. 5.1  | SoC interconnection types: a Shared bus, b Point-to-Point,                                 |     |

|           | <b>c</b> NoC                                                                               | 110 |

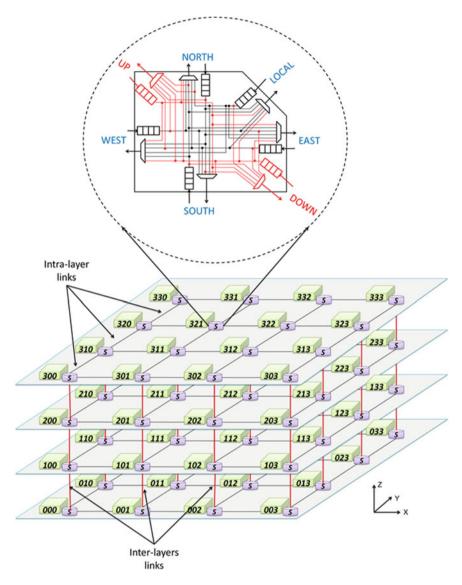

| Fig. 5.2  | Configuration example of a $4 \times 4 \times 4$ 3D-ONoC based on                          |     |

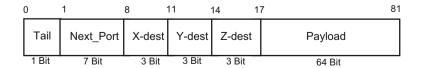

|           | mesh topology                                                                              | 114 |

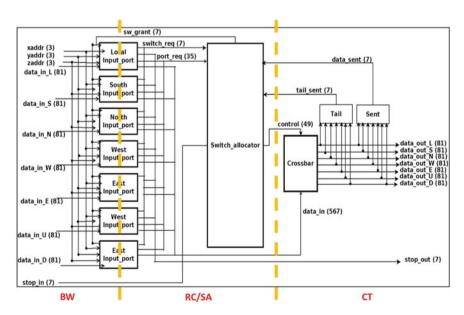

| Fig. 5.3  | 3D-ONOC flit format                                                                        | 116 |

| Fig. 5.4  | 3D-ONoC pipeline stages: buffer writing (BW), routing                                      |     |

|           | calculation and switch allocation (RC/SA) and crossbar                                     |     |

|           | traversal stage (CT)                                                                       | 117 |

| Fig. 5.5  | Input-port module architecture                                                             | 119 |

| Fig. 5.6  | Switch allocator architecture                                                              | 122 |

| Fig. 5.7  | Stall-Go flow control mechanism                                                            | 123 |

| Fig. 5.8  | Stall-Go flow control finite state machine                                                 | 123 |

| Fig. 5.9  | Scheduling matrix priority assignment                                                      | 124 |

| Fig. 5.10 | Crossbar circuit                                                                           | 126 |

| Fig. 5.11 | Network interface architecture: Transmitter side                                           | 128 |

| Fig. 5.12 | Network interface architecture: Receiver side                                              | 130 |

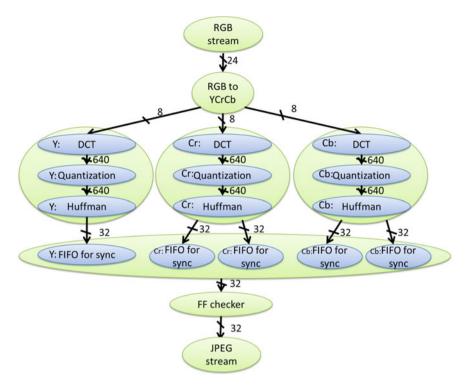

| Fig. 5.13 | Task graph of the JPEG encoder                                                             | 131 |

| Fig. 5.14 | Extended task graph of the JPEG encoder                                                    | 132 |

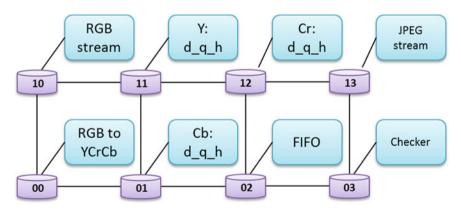

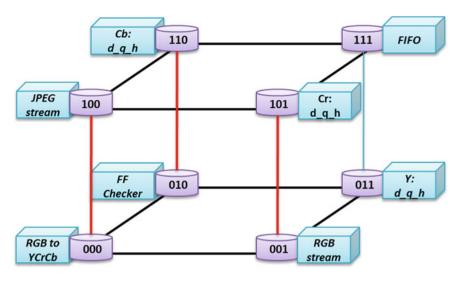

| Fig. 5.15 | JPEG encoder mapped on 2 × 4 2D-ONoC                                                       | 132 |

| Fig. 5.16 | JPEG encoder mapped on $2 \times 2 \times 2$ 3D-ONoC                                       | 133 |

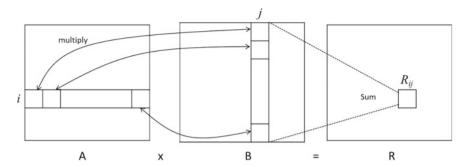

| Fig. 5.17 | Matrix multiplication example: The multiplication of an <i>i</i>                           |     |

| C         | $\times k$ matrix A by a $k \times j$ matrix B results in an $i \times j$ matrix $R \dots$ | 133 |

| Fig. 5.18 | Simple example demonstrating the matrix multiplication                                     |     |

|           | calculation                                                                                | 134 |

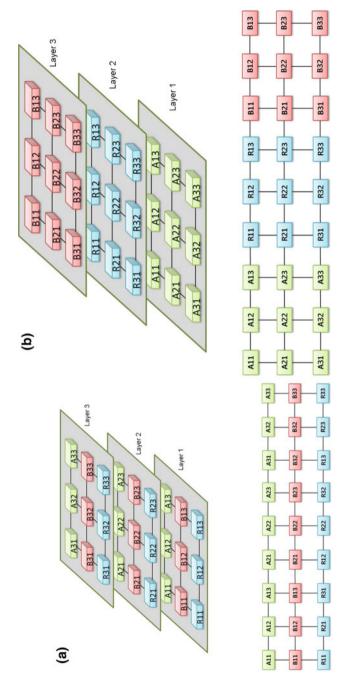

| Fig. 5.19 | $3 \times 3$ matrix multiplication using <b>a</b> optimistic and <b>b</b> pessimistic      |     |

| C         | mapping approaches                                                                         | 135 |

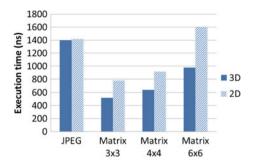

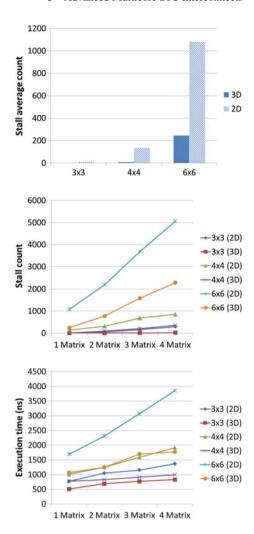

| Fig. 5.20 | Execution time comparison between 3D- and 2D-ONoC                                          | 139 |

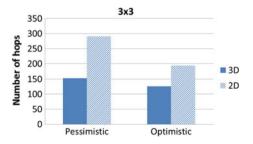

| Fig. 5.21 | Average number of hops comparison for both pessimistic and                                 |     |

| Ü         | optimistic mappings on $3 \times 3$ network size                                           | 140 |

| Fig. 5.22 | Average number of hops comparison for both pessimistic                                     |     |

| C         | and optimistic mappings on 4 × 4 network size                                              | 141 |

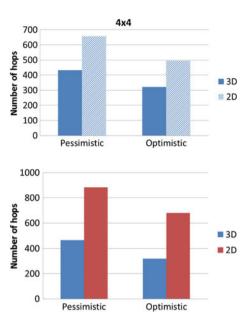

| Fig. 5.23 | Average number of hops comparison for both pessimistic and                                 |     |

| C         | optimistic mappings on $6 \times 6$ network size                                           | 141 |

| Fig. 5.24 | Stall average count comparison between 3D- and 2D-ONoC                                     | 142 |

| Fig. 5.25 | Stall average count comparison between 3D- and 2D-ONoC                                     |     |

| C         | with different traffic loads                                                               | 142 |

| Fig. 5.26 | Execution time comparison between 3D- and 2D-ONoC                                          |     |

| _         | with different traffic loads                                                               | 142 |

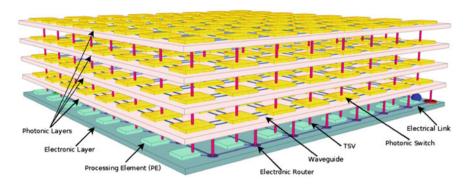

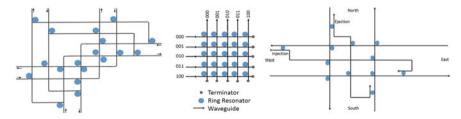

| Fig. 5.27 | 3D-Stacked photonic network-on-chip architecture                                           | 145 |

| Fig. 5.28 | Photonic link architecture                                                                 | 145 |

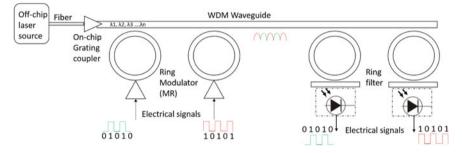

| Fig. 5.29 | Gateway organization                                                                       | 146 |

| $\sim$    | • •                                                                                        |     |

List of Figures xxi

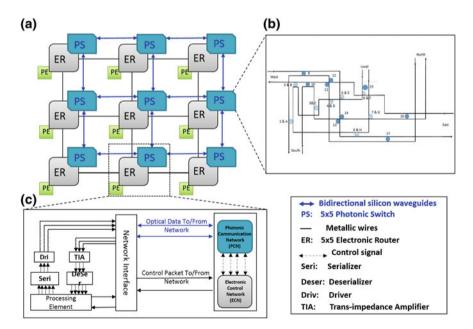

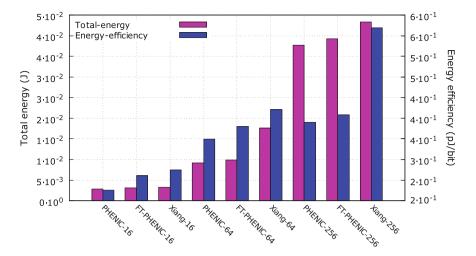

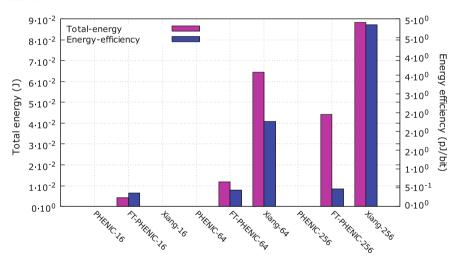

| Fig. 5.30  | FT-PHENIC system architecture. <b>a</b> $3 \times 3$ mesh-based system,             |     |

|------------|-------------------------------------------------------------------------------------|-----|

|            | <b>b</b> $5 \times 5$ non-blocking photonic switch, <b>c</b> Unified tile including |     |

|            | PE, NI, and control modules                                                         | 150 |

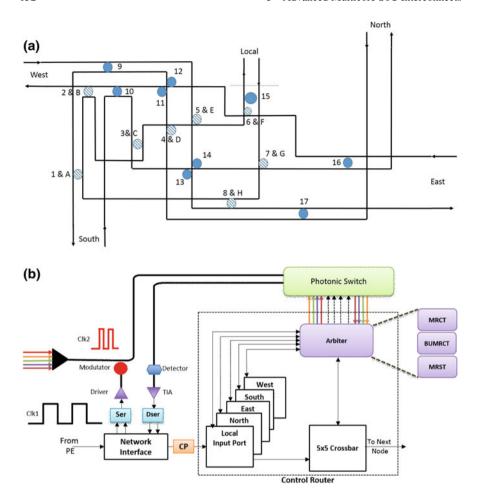

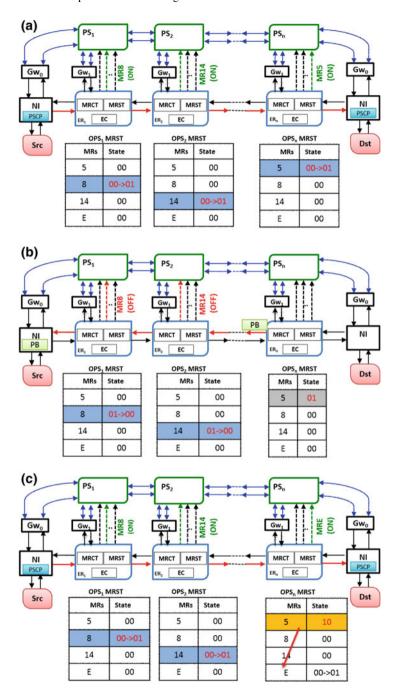

| Fig. 5.31  | Microring fault-resilient photonic router (MRPR):                                   |     |

|            | a Non-blocking fault-tolerant photonic switch, b Light-weight                       |     |

|            | control router                                                                      | 152 |

| Fig. 5.32  | Example of how a non-redundant MR's functionality can be                            |     |

|            | mimicked by redundant ones                                                          | 153 |

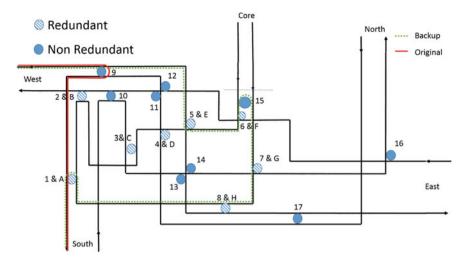

| Fig. 5.33  | Microring fault-resilient path configuration: <b>a</b> Path setup,                  |     |

| C          | <b>b</b> Path-blocked, <b>c</b> Faulty MR with recovery. $GW_0$ : Gateway for       |     |

|            | data, $GW_1$ : Gateway for acknowledgment signals, PS: photonic                     |     |

|            | switch, MRCT: Microring Configuration Table, MRST:                                  |     |

|            | Microring State Table. $00 = \text{Not faulty}$ , Not blocked, $01 = \text{Not}$    |     |

|            | faulty, Blocked, 10 = Faulty                                                        | 157 |

| Fig. 5.34  | Fault-tolerant path-configuration algorithm                                         | 158 |

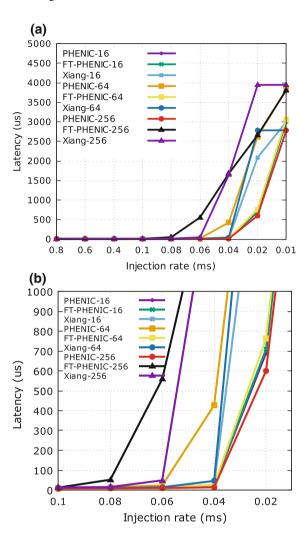

| Fig. 5.35  | Latency comparison results under random uniform traffic:                            |     |

| C          | a Overall Latency, <b>b</b> Latency near saturation                                 | 163 |

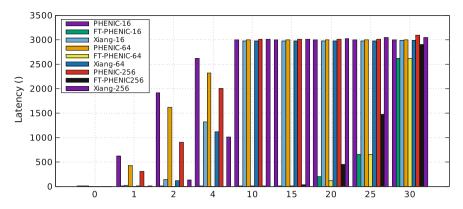

| Fig. 5.36  | Latency results of each system as faults are introduced                             | 164 |

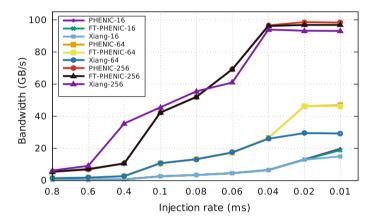

| Fig. 5.37  | Bandwidth comparison results under random uniform traffic                           | 164 |

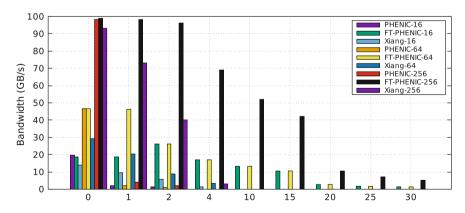

| Fig. 5.38  | Bandwidth comparison results as faults are introduced                               | 164 |

| Fig. 5.39  | Total energy and energy efficiency comparison results under                         |     |

| 8, -, -, - | random uniform traffic near saturation                                              | 165 |

| Fig. 5.40  | Total energy and energy efficiency comparison results under                         |     |

| C          | random uniform traffic with 4% of MRs acting faulty                                 | 165 |

| Fig. 5.41  | Example of photonic switches. From left to right: PHENIC's                          |     |

| <i>6</i> , | original [9], crossbar, and crux [104]                                              | 167 |

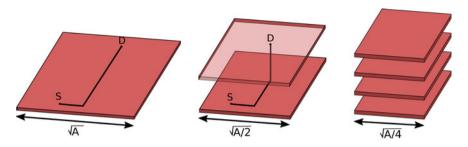

| Fig. 6.1   | Reducing footprint and wire length in 3D-stack structure                            | 176 |

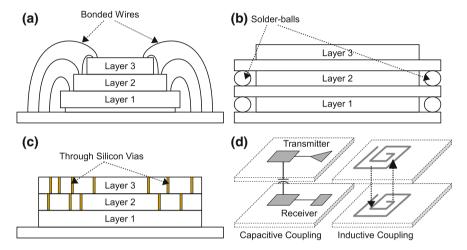

| Fig. 6.2   | 3D integration schemes: <b>a</b> Wire bonding; <b>b</b> Solder balls;               |     |

| C          | c Through silicon vias; d Wireless stacking                                         | 176 |

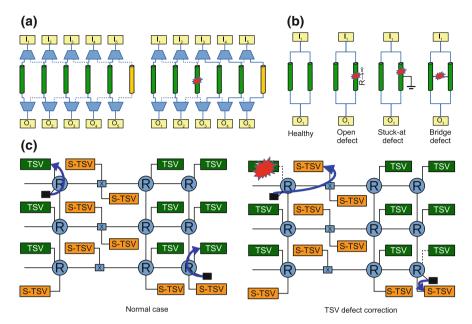

| Fig. 6.3   | TSV fault-tolerance schemes: a Redundancy technique;                                |     |

| <i>G</i> , | <b>b</b> Double TSV; <b>c</b> Network TSV                                           | 178 |

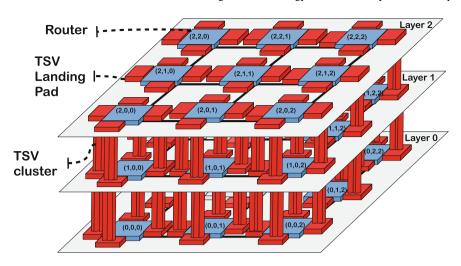

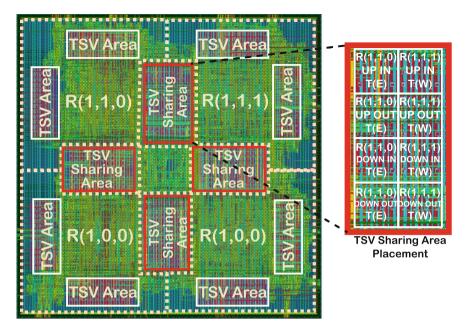

| Fig. 6.4   | High-level view of the system architecture with $3 \times 3 \times 3$               |     |

| C          | configuration                                                                       | 180 |

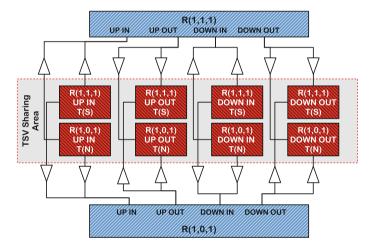

| Fig. 6.5   | TSV sharing area placement and connectivity between two                             |     |

| C          | neighboring routers                                                                 | 180 |

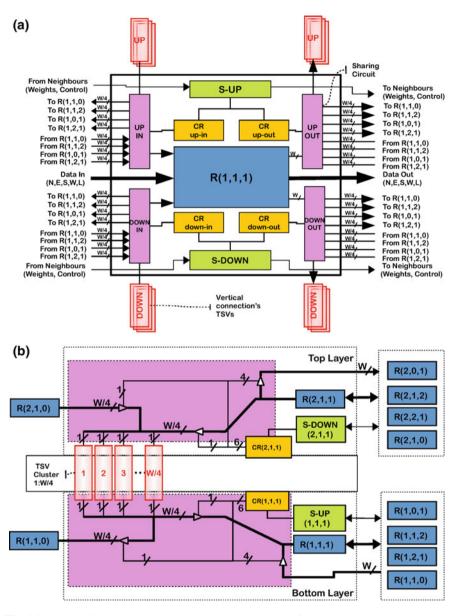

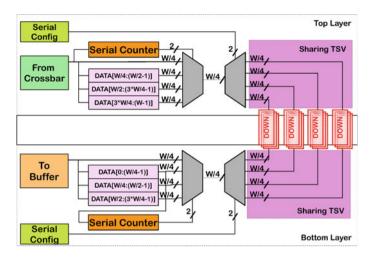

| Fig. 6.6   | The TSV fault-tolerance architecture: <b>a</b> Router wrapper;                      |     |

| C          | <b>b</b> Connection between two layers. <i>Red rectangles</i> represent             |     |

|            | TSVs. S-UP and S-DOWN are the sharing arbitrators which                             |     |

|            | manage the proposed mechanism. CR stands for configuration                          |     |

|            | register and $W$ is the flit width                                                  | 181 |

| Fig. 6.7   | Adaptive online TSV sharing algorithm                                               | 183 |

xxii List of Figures

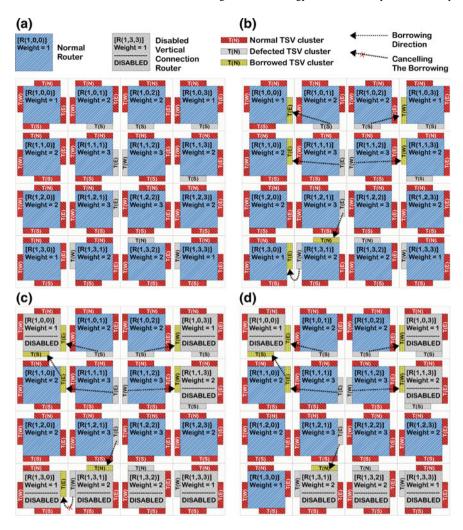

| Fig. 6.8  | An example of the sharing algorithm on a 4 × 4 layer: <b>a</b> Initial state with ten defected TSV clusters; <b>b</b> Best candidates selection; <b>c</b> Borrowing chain creating and selection refining. <b>d</b> Final result with six disabled routers | 184 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 6.9  | Example of the weight adjustment performed to disable routers'                                                                                                                                                                                             | 104 |

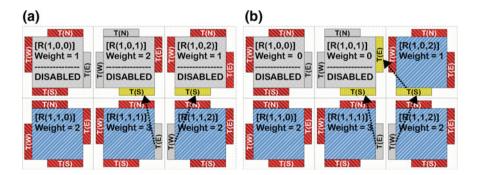

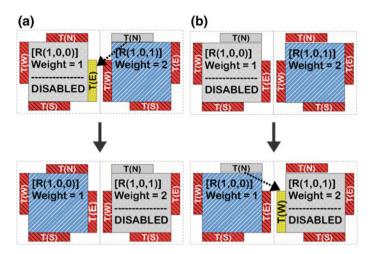

| 11g. 0.7  | sharing: <b>a</b> Before weight update; <b>b</b> After weight update                                                                                                                                                                                       | 186 |

| Fig. 6.10 | Examples of virtual TSV: <b>a</b> return the TSV cluster to the                                                                                                                                                                                            | 100 |

| C         | original router; <b>b</b> borrow a cluster from a higher                                                                                                                                                                                                   |     |

|           | weight router                                                                                                                                                                                                                                              | 188 |

| Fig. 6.11 | Circuit of 1:4 serialization                                                                                                                                                                                                                               | 189 |

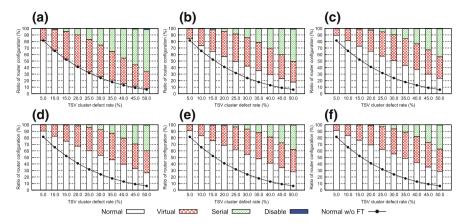

| Fig. 6.12 | Defect-rate evaluation: <b>a</b> Layer size: $2 \times 2$ (4 routers, 16 TSV                                                                                                                                                                               |     |

|           | clusters); <b>b</b> Layer size: $4 \times 4$ (16 routers, 64 TSV clusters);                                                                                                                                                                                |     |

|           | <b>c</b> Layer size: $8 \times 8$ (64 routers, 256 TSV clusters); <b>d</b> Layer                                                                                                                                                                           |     |

|           | size: $16 \times 16$ (256 routers, 1024 TSV clusters); <b>e</b> Layer size:                                                                                                                                                                                |     |

|           | $32 \times 32$ (1024 routers, 4096 TSV clusters); <b>f</b> Layer size:                                                                                                                                                                                     |     |

|           | 64 × 64 (4096 routers, 16384 TSV clusters)                                                                                                                                                                                                                 | 191 |

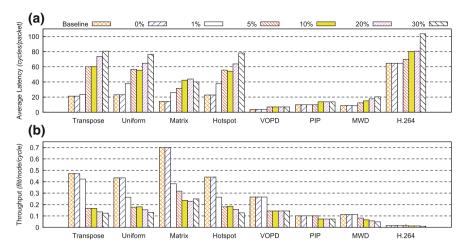

| Fig. 6.13 | Evaluation result: <b>a</b> Average packet latency; <b>b</b> Throughput                                                                                                                                                                                    | 193 |

| Fig. 6.14 | Single layer layout illustrating the TSV sharing areas                                                                                                                                                                                                     | 405 |

| T         | (red boxes). The layout size is $865 \mu m \times 865 \mu m$                                                                                                                                                                                               | 195 |

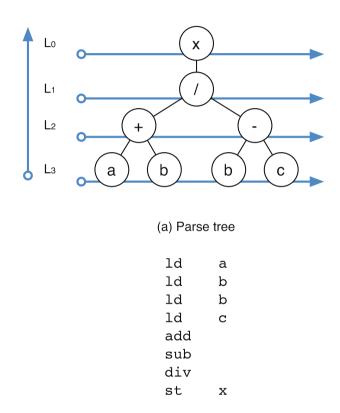

| Fig. 7.1  | Instruction sequence generation from the parse tree of                                                                                                                                                                                                     |     |

|           | expression $x = \frac{a+b}{b-c}$                                                                                                                                                                                                                           | 205 |

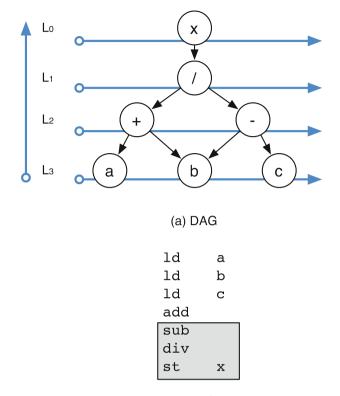

| Fig. 7.2  | Instruction sequence generation from DAG of expression                                                                                                                                                                                                     |     |

|           | $x = \frac{a+b}{b-c} \dots \dots$                                                                                                                    | 207 |

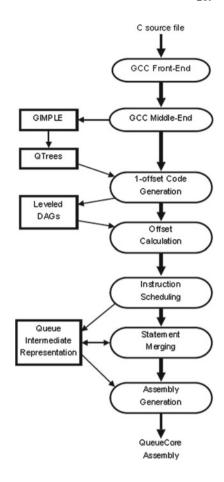

| Fig. 7.3  | Parallelizing compiler infrastructure                                                                                                                                                                                                                      | 209 |

| Fig. 7.4  | QIR code fragment                                                                                                                                                                                                                                          | 214 |

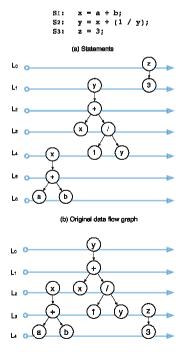

| Fig. 7.5  | Statement merging transformation                                                                                                                                                                                                                           | 215 |

| Fig. 7.6  | Assembly output for QueueCore processor                                                                                                                                                                                                                    | 216 |

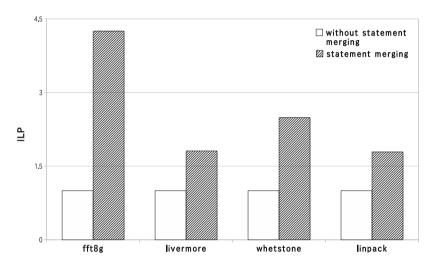

| Fig. 7.7  | Effect on ILP of statement merging transformation in the queue                                                                                                                                                                                             | 210 |

| F: 70     | compiler                                                                                                                                                                                                                                                   | 218 |

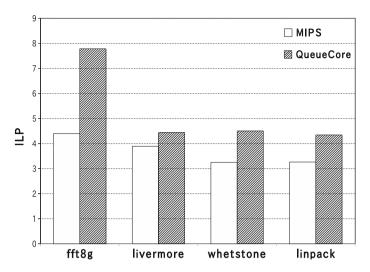

| Fig. 7.8  | Instruction level parallelism improvement of queue compiler                                                                                                                                                                                                | 220 |

| E:- 7.0   | over optimizing compiler for a RISC machine                                                                                                                                                                                                                | 220 |

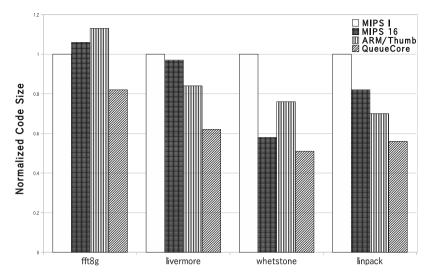

| Fig. 7.9  | Normalized code size for two embedded RISC processors and QueueCore                                                                                                                                                                                        | 221 |

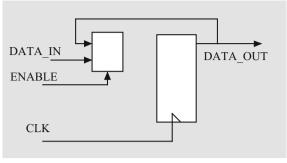

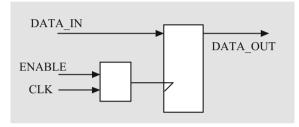

| Fig. 8.1  | Clock gating example                                                                                                                                                                                                                                       | 231 |

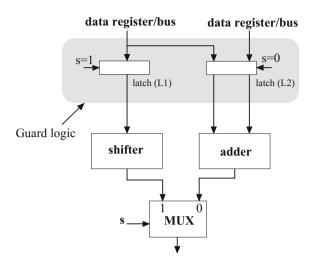

| Fig. 8.2  | Dual operation ALU with guard logic. The multiplexer does                                                                                                                                                                                                  | 231 |

| 1 ig. 0.2 | the selection only after both units have completed their                                                                                                                                                                                                   |     |

|           | evaluation. The evaluation of one of the two units is avoided by                                                                                                                                                                                           |     |

|           | using a guard logic; two latches (L1 and L2) are placed with                                                                                                                                                                                               |     |

|           | enable signals (s1 and s2) at the inputs of the shifter and the                                                                                                                                                                                            |     |

|           | adder respectively                                                                                                                                                                                                                                         | 232 |

| Fig. 8.3  | Power consumption in typical processor core                                                                                                                                                                                                                | 235 |

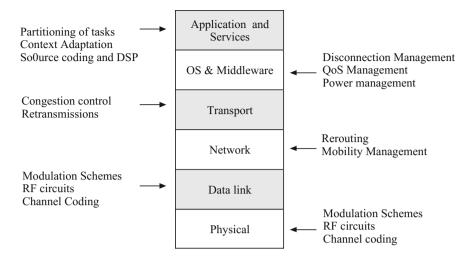

| Fig. 8.4  | Protocol stack of a generic wireless network, and                                                                                                                                                                                                          |     |

| <i>6</i>  | corresponding areas of energy-efficient possible research                                                                                                                                                                                                  | 240 |

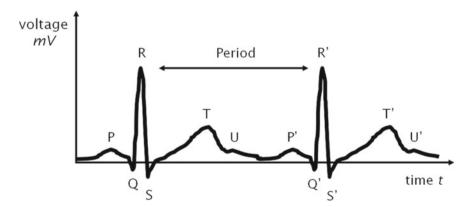

| Fig. 9.1  | A typical ECG wave                                                                                                                                                                                                                                         | 247 |

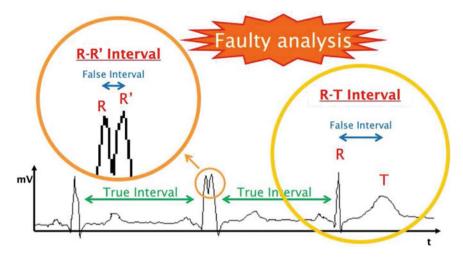

| Fig. 9.2  | Faulty ECG Analysis                                    | 252 |

|-----------|--------------------------------------------------------|-----|

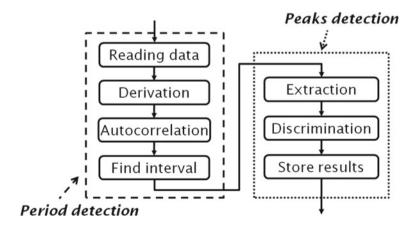

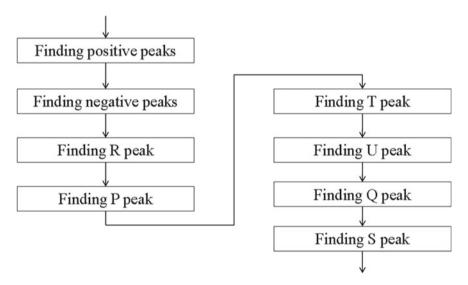

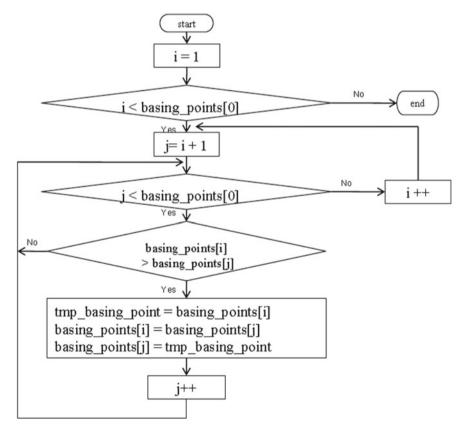

| Fig. 9.3  | PPD algorithm processing flow                          | 252 |

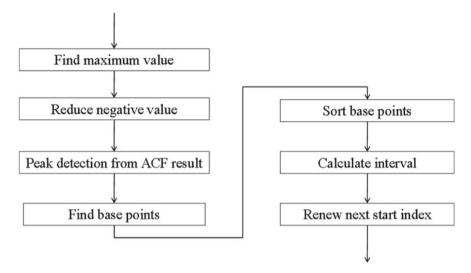

| Fig. 9.4  | Period detection computation details                   | 254 |

| Fig. 9.5  | Peaks detection computation details                    | 254 |

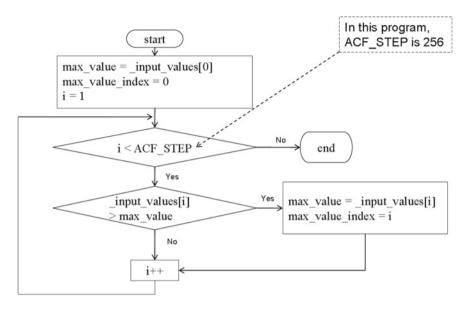

| Fig. 9.6  | Period detection: finding maximum value algorithm. The |     |

|           | autocorrelation step ACF_STEP is set 256               | 255 |

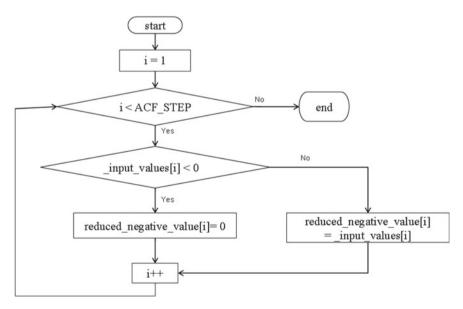

| Fig. 9.7  | Period detection: reduce negative value algorithm      | 255 |

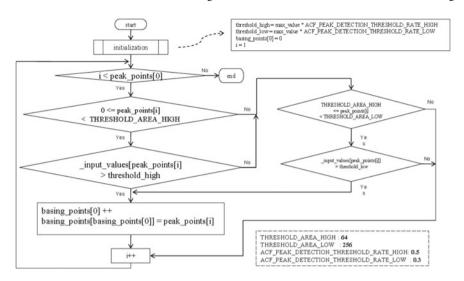

| Fig. 9.8  | Period detection: find base points                     | 256 |

| Fig. 9.9  | Period detection: sort base points                     | 256 |

| Fig. 9.10 | High-level view of the BANSMOM system architecture     | 257 |

| Fig. 9.11 | Prototyped multicore SoC block diagram                 | 260 |

| Fig. 9.12 | Nios II core architecture block diagram                | 260 |

| Fig. 9.13 | Software simulation output                             | 262 |

| Fig. 9.14 | (a) Get live-data, (b) Get previous-data               | 263 |

| Fig. 9.15 | Multicore SoC system running snapshot                  | 264 |

| Fig. 9.16 | Interactive RTI tool displaying ECG waves              | 264 |

### **List of Tables**

| Table 2.1  | Linked task description                                        | 27  |

|------------|----------------------------------------------------------------|-----|

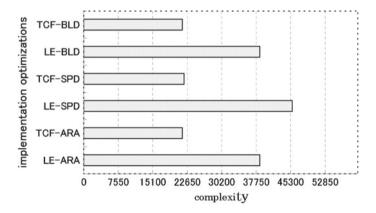

| Table 2.2  | QC-2 processor design results: modules complexity as LE        |     |

|            | (logic elements) and TCF (total combinational functions) when  |     |

|            | synthesized for FPGA (with Stratix device) and                 |     |

|            | Structured ASIC (HardCopy II) families                         | 34  |

| Table 3.1  | Cache coherence states                                         | 64  |

| Table 4.1  | Area utilization for a 5-ports router                          | 91  |

| Table 4.2  | Area utilization for 6-port router                             | 92  |

| Table 4.3  | Flit Types and Coding                                          | 98  |

| Table 4.4  | Summary of decisions for distributed routing NI                | 100 |

| Table 5.1  | Simulation parameters                                          | 136 |

| Table 5.2  | 3D-ONoC hardware complexity compared with 2D-ONoC              | 137 |

| Table 5.3  | Microring configuration for normal data transmission           | 153 |

| Table 5.4  | Microring backup configuration for data transmission           | 154 |

| Table 5.5  | Wavelength assignment for acknowledgment signal                |     |

|            | (Mod: Modulator, and Det: Photodetector)                       | 154 |

| Table 5.6  | Various switches and their estimated losses. AL: Average Loss, |     |

|            | WL: Worst Loss                                                 | 155 |

| Table 5.7  | Insertion loss parameters for 22 nm process                    | 155 |

| Table 5.8  | Configuration parameters                                       | 160 |

| Table 5.9  | Photonic communication network energy parameters               | 161 |

|            | MR requirement comparison results for 64 cores systems         | 161 |

| Table 5.11 | MRs requirement comparison results for 256-core systems        | 162 |

| Table 6.1  | Configuration register (CR) description                        | 182 |

| Table 6.2  | Technology parameters                                          | 189 |

| Table 6.3  | System configurations                                          | 190 |

| Table 6.4  | Simulation configurations                                      | 192 |

| Table 6.5  | Hardware complexity of a single router                         | 194 |

| Table 6.6  | Comparison results between the proposed approach               |     |

|            | and the existing works                                         | 196 |

xxvi List of Tables

| Table 7.1 | Lines of C code for each phase of the queue                  |     |

|-----------|--------------------------------------------------------------|-----|

|           | compiler's back end                                          | 218 |

| Table 7.2 | Instruction category percentages for the compiled benchmarks |     |

|           | for the QueueCore                                            | 219 |

| Table 7.3 | QueueCore's program maximum offset reference value           | 219 |

| Table 8.1 | Operating system functionality and corresponding techniques  |     |

|           | for optimizing energy utilization                            | 236 |

| Table 9.1 | Hardware complexity                                          | 265 |

| Table 9.2 | Performance evaluation                                       | 265 |

# **Chapter 1 Introduction to Multicore Systems On-Chip**

**Abstract** Systems On-Chip (SoCs) designs have evolved from fairly simple unicore, single memory designs to complex heterogeneous multicore SoC architectures consisting of large number of IP blocks on the same silicon. To meet high computational demands posed by latest consumer electronic devices, most current systems are based on such paradigm, which represents a real revolution in many aspects in computing. This chapter presents a general introduction to the multicore System-On-Chip (MCSoCs). We start this chapter by describing the needs for multicore systems by today's general and embedded application domains. Design challenges and basics multicore SoCs hardware and software design are also described.

#### 1.1 The Multicore Revolution

The major chip manufacturers and processor architects have historically invested time and money in micro-architectural and performance enhancements. Many of these efforts such as deep pipelining, increased large cache size, and sophisticated dynamic ILP (Instruction Level Parallelism) extraction exhibit diminishing returns due to increased area and power consumption. When considering the limitations associated with voltage supply scaling, threshold scaling, and clock frequency scaling, along with the above design complexity, architects were already looking for an alternative to the single-core approach. Multicore was therefore the natural next revolution in staying on the ever increasing performance driven curve. But, was it really the good timing to switch from uni-processor approach to the more complex parallel structure of multiprocessor/multicore platforms? The direct answer from major hardware companies was very clear: yes; it is time for revolution and not for evolution! This important decision was fueled by the shift that started from around 2004 when market leaders in the production of general purpose computer systems and embedded devices started offering an increasing number of cores (processors), in which multiple cores communicate directly through shared hardware caches, providing high concurrency instead of high clock speed. This shift contributed to an unprecedented paradigm that has led to what is know today as multicore revolution.

1

The main reason behind this shift can be simply explained by the limits of process technologies. As the computing needs of each processor type grew year by year, the traditional response by the semiconductor industries was to increase the clock frequency of the processor core. However, as processor frequencies increase, other issues such as power consumption, thermal power, the inability to find sufficient parallelism in the program and lagging memory bandwidth become real obstacles to further advancements.

In a typical multicore SoC system, a single physical chip integrates various components together. The single chip may contains digital, analog, mixed-signal, and often radio-frequency functions. Further, each individual core can run at a lower speed, which reduces overall power consumption as well as heat generation. For example, Intel Polaris multicore chip contains 80 cores, each containing two programmable floating point engines and one five-port messaging passing router [1]. This integration approach offers significant price, performance, and flexibility over higher speed single-core processor design.

#### 1.1.1 The Impact of Moore's Law

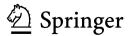

One of the guiding principles of computer architecture is known as Moore's Law. In April 1965, Gordon Moore wrote an article for Electronics magazine titled [Cramming more components onto integrated circuits] [2]. He predicted that the number of transistors on a chip would double every 12 months into the near future. Although this exponential trend has gradually lessen to doubling transistors every 18 months, it remains the driving force behind the integrated circuits industry. This law over the years has provided a road-map for product designers as they plan efficient and better usage of the transistors at their disposal. Figure 1.1 shows the scaling of transistor count and operating frequency in ICs [3].

#### 1.1.2 On-Chip Interconnection Schemes

Shared bus was is still the dominant interconnect structure for simple SoC systems. Most buses are bidirectional and devices can send or receive information. The good benefit in bus is that it allows to add new devices easily and facilitates portabilities of peripheral devices between different systems. However, if too many cores are connected to the same bus, the bandwidth of the bus, clock skew and delay can become the bottlenecks.

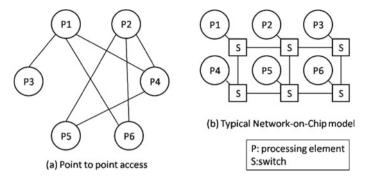

A new interconnection scheme, known as on-chip network, or NoC, based on *packet switching* approach was proposed [4–6]. NoCs are becoming an attractive option for solving shared bus problems. NoC is a scalable architectural platform with huge potential to handle growing complexity (dozens of cores) and can provide easy reconfigurability, and scalability. The basic idea of NoC is that cores are connected

Fig. 1.1 Scaling of transistor counts and operating frequency in ICs. The feature size and design abstraction are also shown in the graph

via a *packet switching* communication on a single chip—similar to the way computers are connected to Internet.

The *packet switching* scheme supports asynchronous transfer of information. Yet, it provides extremely high bandwidth by distributing the propagation delay across multiple switches; thus pipelining the signal transmission. In addition, NoC offers several promising features. First, it transmits packets instead of words. Thus, dedicated address line like in bus systems are not necessary since the destination address of a packet is part of the packet itself. Second, transmission can be conducted in parallel if the network provides more than one transmission channel between a sender and a receiver. Thus, unlike bus-based system, NoC presents theoretical infinite scalability, facilitate IP core reusing, and higher parallelism.

During the last few years, several research groups adopted various concepts from conventional parallel and distributed (Internet) computing world and investigated various design issues related to NoCs. Chapters 4, 5, and 6 will present architecture and design details of such promising interconnects.

#### 1.1.3 Parallelism and Performance

The prevalence of multicore and many-core technologies has brought ubiquitous parallelism and a huge theoretical potential for intensive tasks. Parallelism issue is now affecting all kinds of software development processes. Further, as software, hardware, and applications have evolved, there is a real need to run multiple such tasks simultaneously to benefit from the available hardware capability in multicore and many-core based systems. Thus, a good multicore programming model should be developed and should exploit all types of available parallelism (ILP, DLP, TLP, CLP, etc.) to maximize performance. For example, multimedia applications today often consist of multiple threads or processes. Recall that a thread can be defined as a basic unit of CPU utilization. It consists of a program counter register (PC), CPU state information for the current thread, and other resources such as a Stack (lastin-first-out data structure). However, finding and scheduling parallel instructions or threads is not an easy task since most applications and algorithms are not yet ready to utilize available multicore capabilities.

Most embedded applications are computation-intensive or/and data-intensive types and can only benefit from the full multicore SoC hardware potential if all features on the system level are taken into account. In addition, programmer should exploit different level of parallelisms which are found at several levels in the system. Existing approaches require the programmer/compiler to identify the parallelism in the program and statically create a parallel program using a programming model such as Pthreads (POSIX Threads) [7], MPI (Message Passing Interface) [8], or task programming, expressed in an a high-level language such as C. There are different types of parallelism that a programmer can exploit

- Bit-Level Parallelism (BLP): Bit-Level Parallelism extends the hardware architecture to operate simultaneously on larger data. However, by extending the word length from, for example 8–16, the operation can now be executed by a single operation. This is of course good for performance. Thus, word length has doubled from 4-bit processors through 8, 16, and even 64-bit in advanced processor cores.

- Instruction-Level Parallelism (ILP): ILP is a well known and is (was) an efficient technique for identifying independent instructions and executing them in parallel. Generally, the compiler takes care about finding independent instructions and schedule them for execution by the hardware. Other known techniques are speculative and out-of-order (OoO) execution which are implemented in hardware. Because programs are written in sequential manner, finding independent instructions is not always possible. Some applications, such as for signal processing, can function efficiently and several existing DSP cores can execute eight or even more instructions per cycle and per core (inst/cycle/core).

- Thread-Level Parallelism (TLP): TLP is a software capability that enables a program, often a high-end program to work with multiple threads at the same time instead of having to wait on other threads. TLP can be exploited in single core or also in multicore systems. If used in multicore system, it allows closely coupled cores that share the same memory to run in parallel on shared data structures.

- Task-Level Parallelism (TaLP): TaLP (also known as function parallelism and control parallelism) focuses on distributing execution processes (or threads) across different parallel cores on the same or different data. Most real programs fall somewhere on a continuum between task parallelism and data parallelism. The difficulty with task parallelism is not on how to efficiently distribute the threads, rather is with how to divide the application program into multiple tasks. TaLP approach allows more independent processes to run in parallel, occasionally exchanging messages.

- Data-Level Parallelism (DLP): DLP (also known as loop-level parallelism) allows multiple units to process data concurrently. One such technique implemented in hardware is SIMD (single instruction multiple data). In multiprocessor/multicore system, data parallelism is achieved when each core performs the same task on different pieces of distributed data. Data parallelism is where multicore plays an important role. Performance improvement depends on how many cores are able to work on the data at the same time. For example, consider adding two matrices using two cores (core0 and core1). In a data parallel implementation, core0 could add all elements from the top half of the matrices, while core1 could add all elements from the bottom half of the matrices. Since the two cores work in parallel, the job of performing matrix addition would take one half the time of performing the same operation in serial using one single core.

Since multicore-based systems mainly exploit TLP approach (of course ILP can be also exploited within a single core in a given multicore-based system), we will only focus on this parallelization technique. In order to support TLP, there are several software and hardware approaches that can be used. One approach involves using a preemptive multitasking operating system (OS). This approach involves the use of an interrupt mechanism which suspends the currently executing process and invokes the OS scheduler to determine which process should be executed next. As a result, all processes will get some amount of CPU time at any given time. The OS kernel can also initiate a context switch to satisfy the scheduling policy's priority constraint, thus preempting the active task. The other known approach to address TLP is called Time-slice multi-threading. This approach allows software developers to hide the latency associated with I/Os by interleaving the execution of multiple threads. But the main problem of this approach is that it does not allow for parallel execution, because only one instruction stream can run on a processor at a time.

A more efficient approach for TLP is called simultaneous multi-threading (SMT), or hyper-threading (HT) as called by Intel [9]. The goal of this approach is to efficiently utilize system's resources. SMP makes a single processor appears, from the programmer's view, as multiple logical processor cores. This means, instructions from more than one thread can be executing in any given pipeline stage at a time. This is done without great changes to the main basic building blocks of a processor.