# INTERNATIONAL EDITION

THE 80x86 IBM PC AND COMPATIBLE COMPUTERS (VOLUMES I & II)

ASSEMBLY LANGUAGE, DESIGN, AND INTERFACING

4th Edition

To view the website that accompanies this text, please go to http://www.prenhall.com/mazidi

# THE 80x86 IBM PC AND COMPATIBLE COMPUTERS (VOLUMES I & II)

ASSEMBLY LANGUAGE, DESIGN, AND INTERFACING

Muhammad Ali Mazidi Janice Gillispie Mazidi

Praised by experts for its clarity and topical breadth, this visually appealing text provides an easy-to-understand, systematic approach to teaching the fundamentals of 80x86 assembly language programming and PC architecture. It offers readers a fun, hands-on learning experience and reinforces concepts with numerous examples and review questions. It uses the Debug utility to show what action the instruction performs, and then provides a sample program to show its application. The text delves into architecture, supporting chips, buses, interfacing techniques, system programming, hard disk characteristics, and more.

## The fourth edition:

- Covers all the 80x86 microprocessors from the 8088 to the Pentium Pro.

- Combines assembly and C programming, and covers C programming in the last section of each chapter.

- Introduces the 80x86 instructions with examples of how they are used.

- Ensures a basic understanding of binary and hex numbering systems.

- Discusses and analyzes hardware differences among 8086, 286, 386, 486, Pentium, and Pentium Pro chips.

- Discusses 8-bit, 16-bit, and 32-bit interfacing of 80x86 microprocessors.

- Shows a real-world approach to PC system programming by using fragments of programs from the IBM PC technical reference.

- Provides an overview of the USB bus.

This is a special international edition of an established title widely used by colleges and universities throughout the world. Pearson Education International published this special edition for the benefit of students outside the United States and Canada.

If you purchased this book within the United States or Canada you should be aware that it has been wrongfully imported without the approval of the Publisher or the Author.

Pearson International Edition

Pearson Education

Not for Sale in the U.S.A. or Canada

# THE 80x86 IBM PC AND COMPATIBLE COMPUTERS

## **VOLUMES I & II**

Assembly Language, Design, and Interfacing

**Fourth Edition**

# THE 80x86 IBM PC AND COMPATIBLE COMPUTERS

## **VOLUMES I & II**

## Assembly Language, Design, and Interfacing

**Fourth Edition**

Muhammad Ali Mazidi Janice Gillispie Mazidi

Pearson Education International

If you purchased this book within the United States or Canada you should be aware that it has been wrongfully imported without the approval of the Publisher or the Author.

Editor in Chief: Stephen Helba

Assistant Vice President and Publisher: Charles E. Stewart, Jr.

Production Editor: Alexandrina Benedicto Wolf

Design Coordinator: Diane Ernsberger

Cover Designer: Jeff Vanik Cover image: Digital Images

Production Manager: Matthew Ottenweller

Marketing Manager: Ben Leonard

This book was set in Times Roman by Janice Mazidi. It was printed and bound by Courier/Kendallville. The cover was printed by Phoenix Color Corp.

Pearson Education LTD.

Pearson Education Australia PTY, Limited

Pearson Education Singapore, Pte. Ltd

Pearson Education North Asia Ltd

Pearson Education Canada, Ltd.

Pearson Educación de Mexico, S.A. de C.V.

Pearson Education -- Japan

Pearson Education Malaysia, Pte. Ltd

Pearson Education, Upper Saddle River, New Jersey

Earlier edition © 1995 by Muhammad Ali Mazidi and Janice Gillispie Mazidi

Copyright © 2003, 2000, 1998 by Pearson Education, Inc., Upper Saddle River, New Jersey 07458. All rights reserved. Printed in the United States of America. This publication is protected by Copyright and permission should be obtained from the publisher prior to any prohibited reproduction, storage in a retrieval system, or transmission in any form or by any means, electronic, mechanical, photocopying, recording, or likewise. For information regarding permission(s), write to: Rights and Permissions Department.

Regard man as a mine rich in gems of inestimable value.

Education can, alone, cause it to reveal its treasures, and enable mankind to benefit therefrom.

Baha'u'llah

## **DEDICATIONS**

This book is dedicated to the memory of Muhammad Ali's parents, who raised 10 children and persevered through more than 50 years of hardship together with dignity and faith.

We feel especially blessed to have the support, love, and encouragement of Janice's parents whose kindness, wisdom, and sense of humor have been the bond that has welded us into a family.

In addition, we must also mention our two most important collaborations: our sons Robert Nabil and Michael Jamal who have taught us the meaning of love and patience.

We would also like to honor the memory of a dear friend, Kamran Lotfi.

## CONTENTS AT A GLANCE

## Assembly Language Programming on the IBM PC, PS, and Compatibles

- 0 INTRODUCTION TO COMPUTING, 1

- 1 THE 80x86 MICROPROCESSOR, 18

- 2 ASSEMBLY LANGUAGE PROGRAMMING, 49

- 3 ARITHMETIC AND LOGIC INSTRUCTIONS AND PROGRAMS, 82

- 4 BIOS AND DOS PROGRAMMING IN ASSEMBLY AND C. 121

- 5 MACROS AND THE MOUSE, 150

- 6 SIGNED NUMBERS, STRINGS, AND TABLES, 173

- 7 MODULES: MODULAR AND C PROGRAMMING, 193

- 8 32-BIT PROGRAMMING FOR 386 AND 486 MACHINES, 220

## Design and Interfacing of the IBM PC, PS, and Compatibles

- 9 8088, 80286 MICROPROCESSOR AND ISA BUS, 235

- 10 MEMORY AND MEMORY INTERFACING, 265

- 11 I/O AND THE 8255; ISA BUS INTERFACING, 309

- 12 INTERFACING TO THE PC: LCD, MOTOR, ADC, AND SENSOR, 351

- 13 8253/54 TIMER AND MUSIC, 386

- 14 INTERRUPTS AND THE 8259 CHIP, 410

- 15 DIRECT MEMORY ACCESSING; THE 8237 DMA CHIP, 447

- 16 VIDEO AND VIDEO ADAPTERS, 477

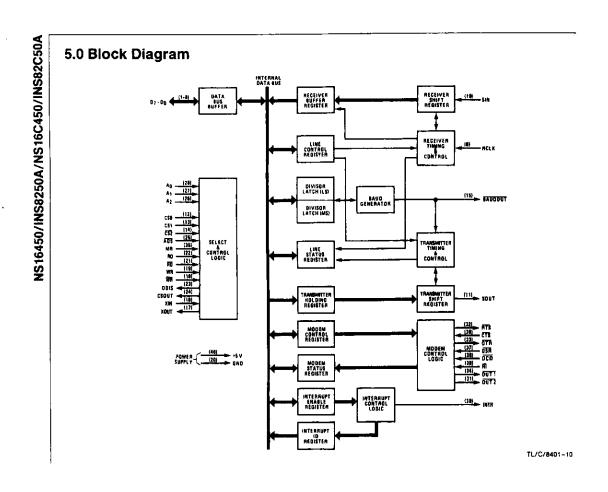

- 17 SERIAL DATA COMMUNICATION AND THE 16450/8250/51 CHIPS, 508

- 18 KEYBOARD AND PRINTER INTERFACING, 541

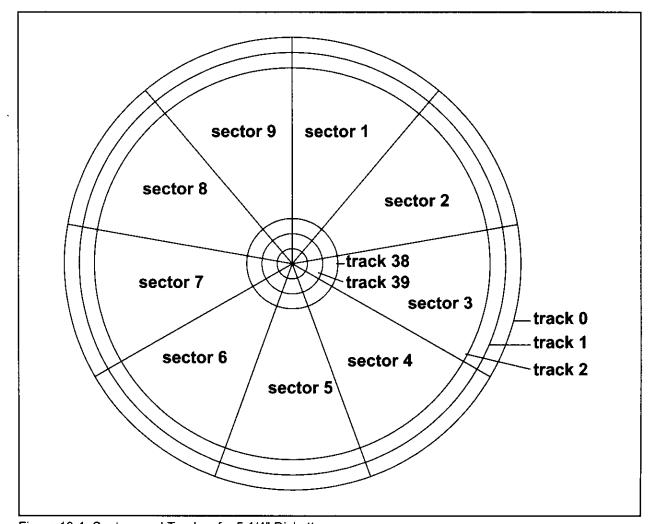

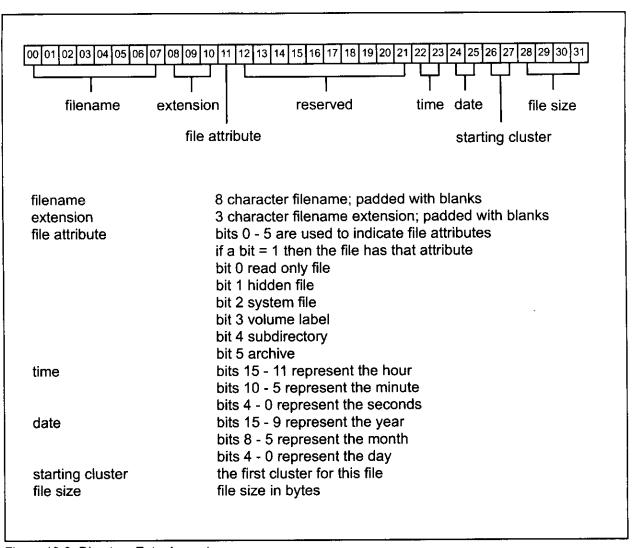

- 19 FLOPPY DISKS, HARD DISKS, AND FILES, 570

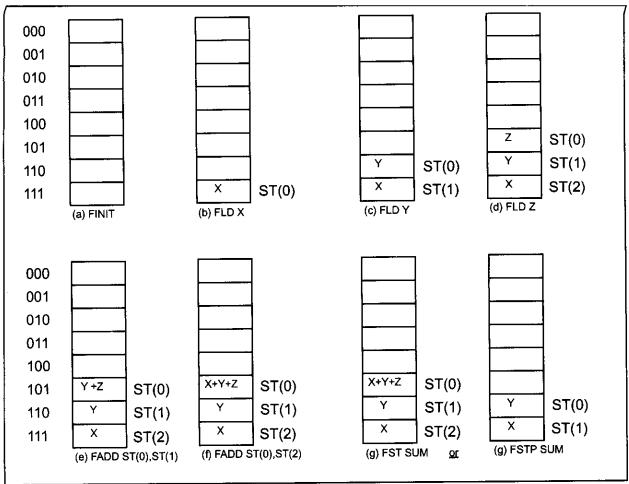

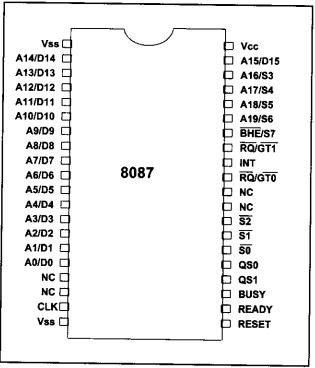

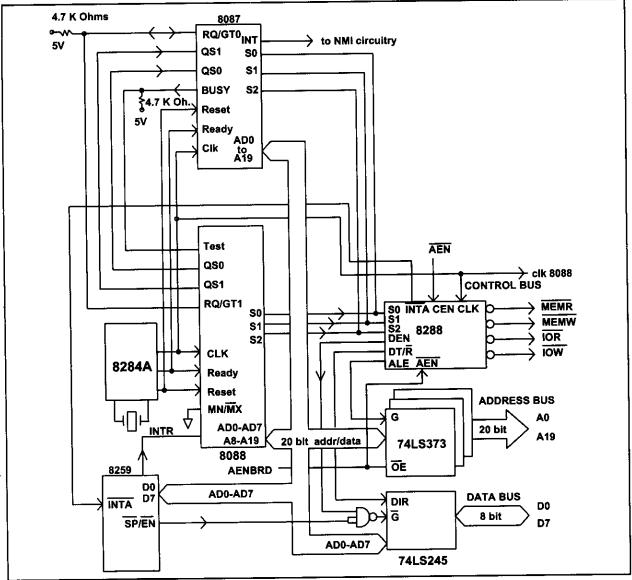

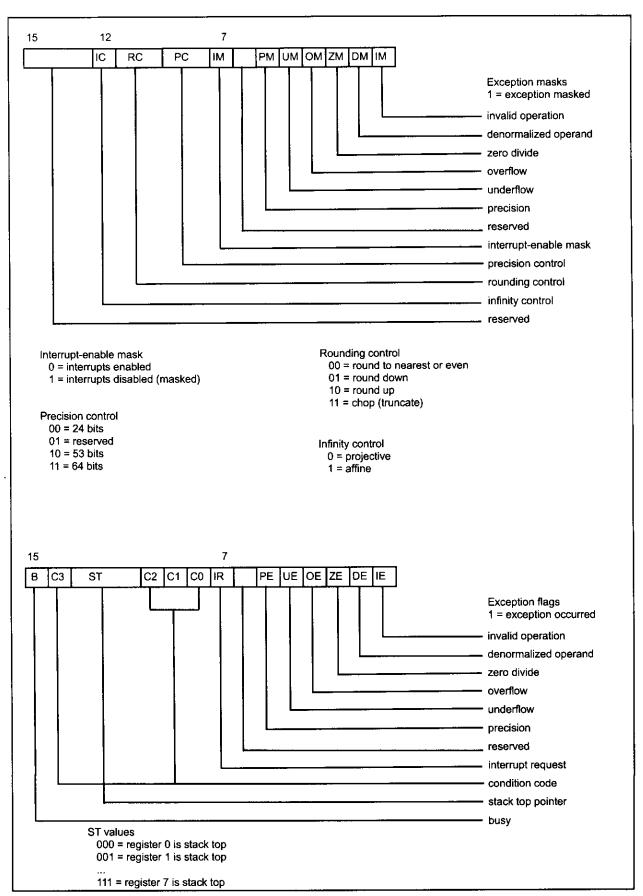

- 20 THE 80x87 MATH COPROCESSOR, 600

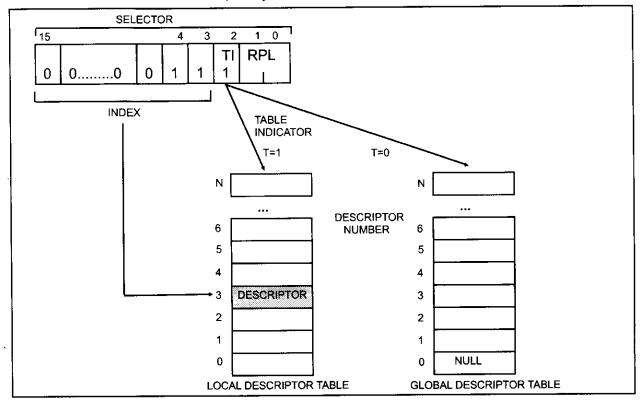

- 21 386 MICROPROCESSOR: REAL VERSUS PROTECTED MODE, 631

- 22 HIGH-SPEED MEMORY INTERFACING AND CACHE, 659

- 23 486, PENTIUM, PENTIUM PRO AND MMX, 690

- 24 MS DOS STRUCTURE, TSR, AND DEVICE DRIVERS, 724

- 25 MS DOS MEMORY MANAGEMENT. 740

- 26 IC TECHNOLOGY AND SYSTEM DESIGN, 759

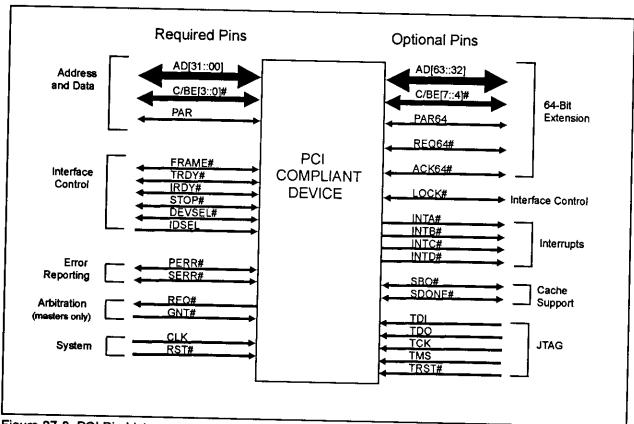

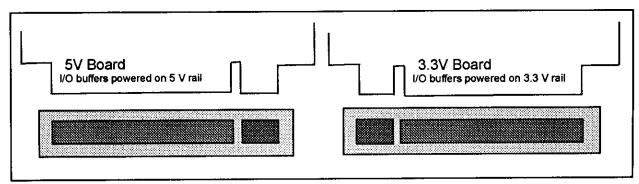

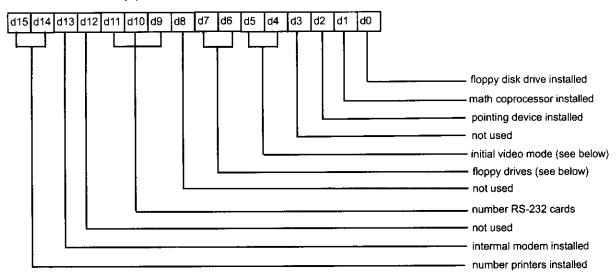

- 27 ISA, PCI, AND USB BUSES, 784

- 28 PROGRAMMING DOS, BIOS, & HARDWARE WITH C/C++, 808

## **APPENDICES**

- A DEBUG PROGRAMMING, 825

- B 80x86 INSTRUCTIONS AND TIMING, 847

- C ASSEMBLER DIRECTIVES AND NAMING RULES, 883.

- D DOS INTERRUPT 21H AND 33H LISTING, 898

- E BIOS INTERRUPTS, 924

- F ASCII CODES, 940

- G I/O ADDRESS MAPS, 941

- H IBM PC/PS BIOS DATA AREA, 952

- I DATA SHEETS, 959

## **CONTENTS**

## PREFACE TO VOLUMES I AND II

| CHAPTER 0: INTRODUCTION TO COMPUTING 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| SECTION 0.1: NUMBERING AND CODING SYSTEMS  Decimal and binary number systems 2  Converting from decimal to binary 2  Converting from binary to decimal 2  Hexadecimal system 3  Converting between binary and hex 4  Converting from decimal to hex 4  Converting from hex to decimal 4  Counting in base 10, 2, and 16 6  Addition of binary and hex numbers 6  2's complement 6  Addition and subtraction of hex numbers 7  Addition of hex numbers 7  Subtraction of hex numbers 7  Subtraction of hex numbers 7  ASCII code 8 | 2  |

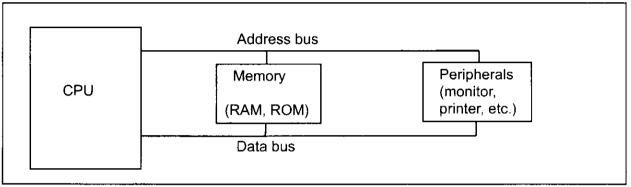

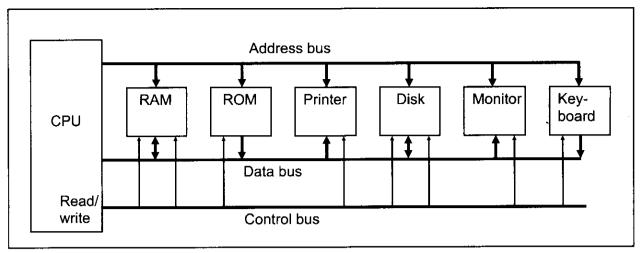

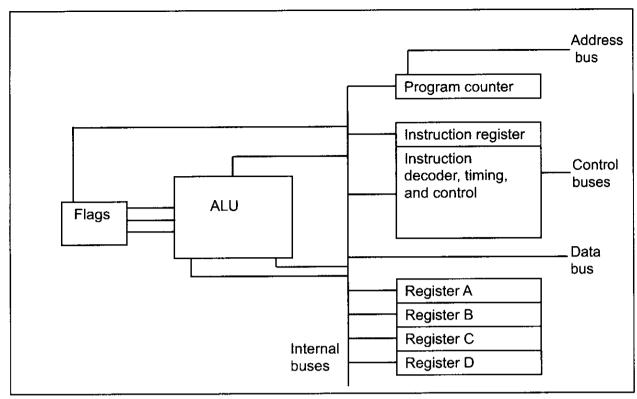

| SECTION 0.2: INSIDE THE COMPUTER 9 Some important terminology 9 Internal organization of computers 9 More about the data bus 10 More about the address bus 10 CPU and its relation to RAM and ROM 11 Inside CPUs 11 Internal working of computers 12  SECTION 0.3: BRIEF HISTORY OF THE CPU 13 CISC vs. RISC 14                                                                                                                                                                                                                   |    |

| CHAPTER 1: THE 80x86 MICROPROCESSOR 18  SECTION 1.1: BRIEF HISTORY OF THE 80x86 FAMILY Evolution from 8080/8085 to 8086 19                                                                                                                                                                                                                                                                                                                                                                                                        | 19 |

| Evolution from 8086 to 8088 19 Success of the 8088 19 Other microprocessors: the 80286, 80386, and 80486                                                                                                                                                                                                                                                                                                                                                                                                                          | 19 |

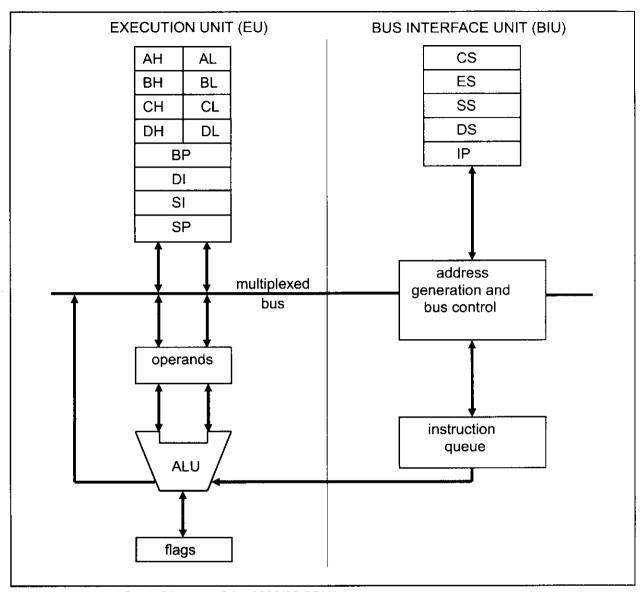

| SECTION 1.2: INSIDE THE 8088/8086 21                     |    |

|----------------------------------------------------------|----|

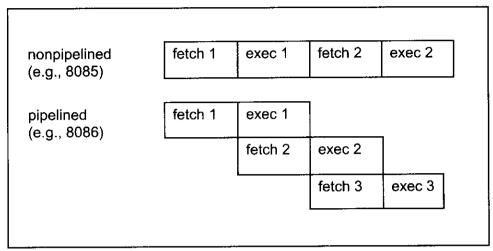

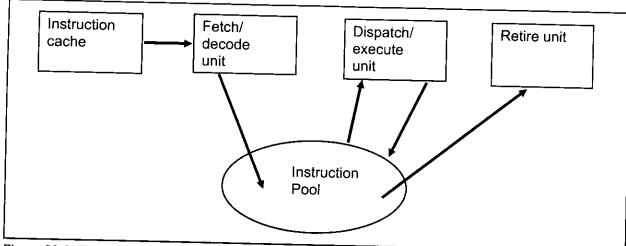

| Pipelining 21                                            |    |

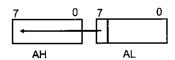

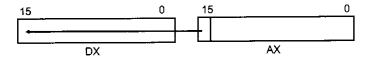

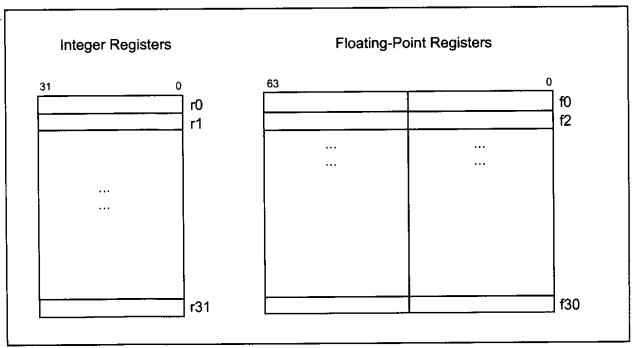

| Registers 22                                             |    |

| · ·                                                      |    |

| SECTION 1.3: INTRODUCTION TO ASSEMBLY PROGRAMMING        | 23 |

| Assembly language programming 24                         |    |

| MOV instruction 24                                       |    |

| ADD instruction 25                                       |    |

| TIDD INSULATION 25                                       |    |

| SECTION 1.4: INTRODUCTION TO PROGRAM SEGMENTS            | 26 |

| Origin and definition of the segment 27                  | 20 |

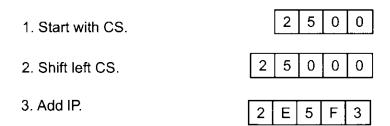

| Logical address and physical address 27                  |    |

| <del>-</del> • •                                         |    |

|                                                          | 20 |

| Logical address vs. physical address in the code segment | 28 |

| Data segment 29                                          | •• |

| Logical address and physical address in the data segment | 30 |

| Little endian convention 31                              |    |

| Extra segment (ES) 32                                    |    |

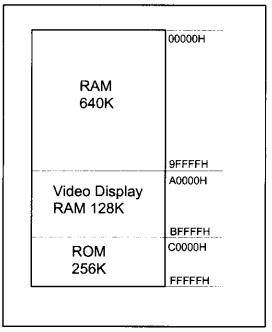

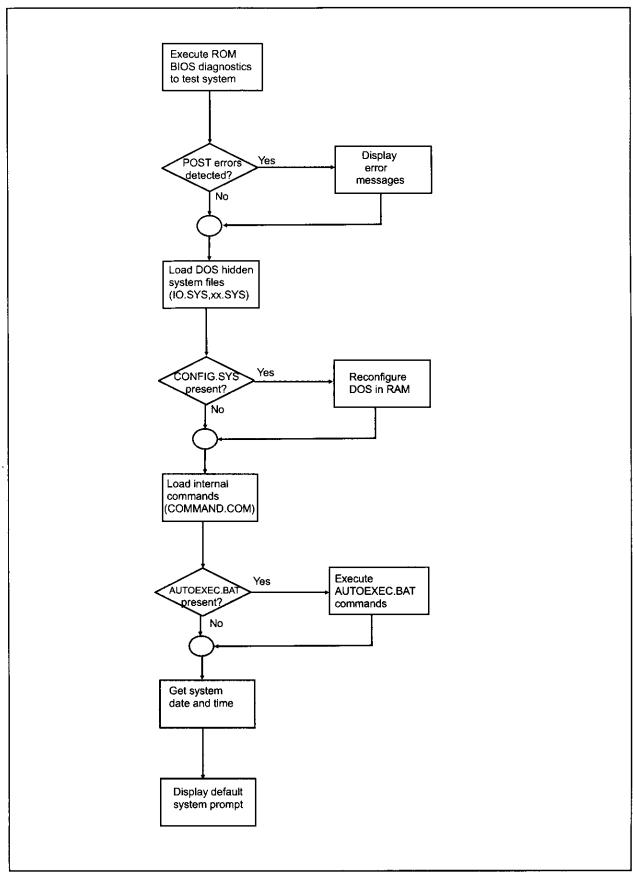

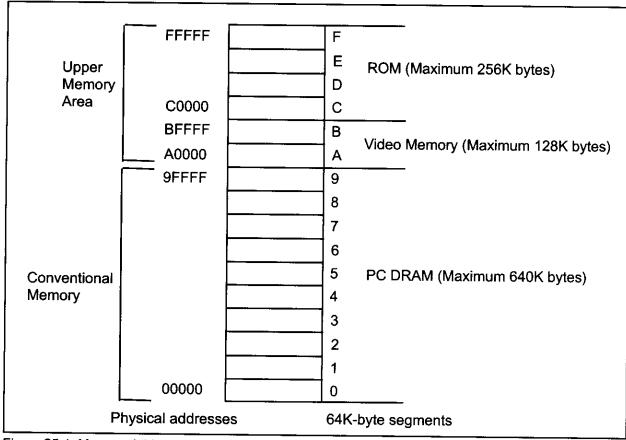

| Memory map of the IBM PC 32                              |    |

| More about RAM 32                                        |    |

| Video RAM 33                                             |    |

| More about ROM 33                                        |    |

| Function of BIOS ROM 33                                  |    |

|                                                          |    |

| SECTION 1.5: MORE ABOUT SEGMENTS IN THE 80x86            | 3  |

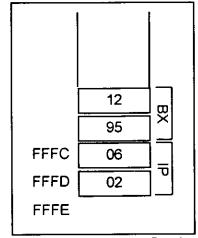

| What is a stack, and why is it needed? 33                |    |

| How stacks are accessed 34                               |    |

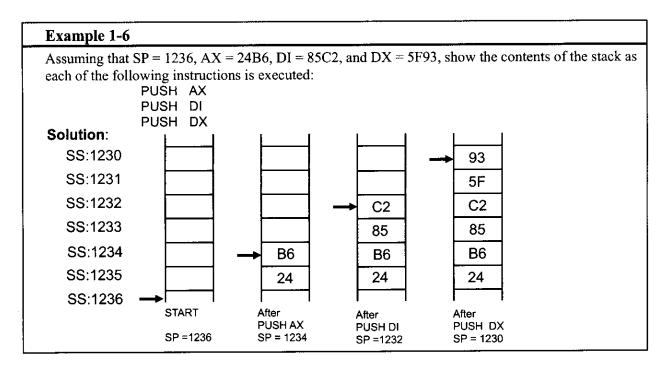

| Pushing onto the stack 34                                |    |

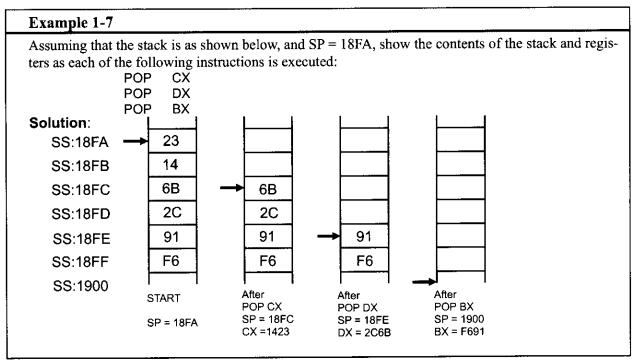

| Popping the stack 34                                     |    |

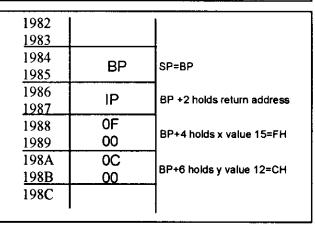

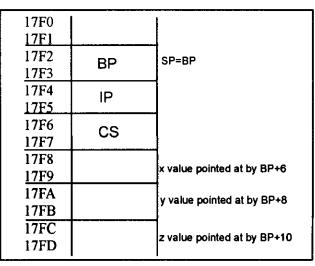

| Logical address vs. physical address for the stack 35    |    |

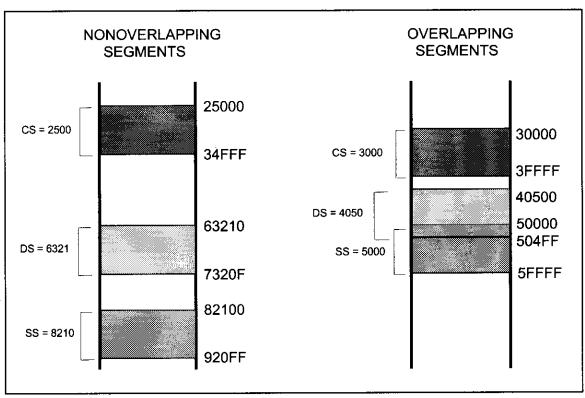

| A few more words about segments in the 80x86 36          |    |

| Overlapping 36                                           |    |

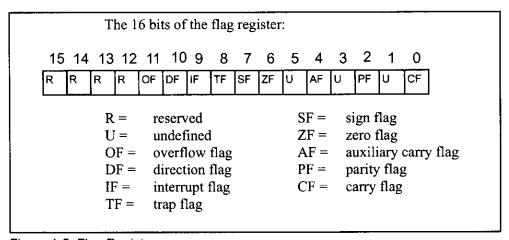

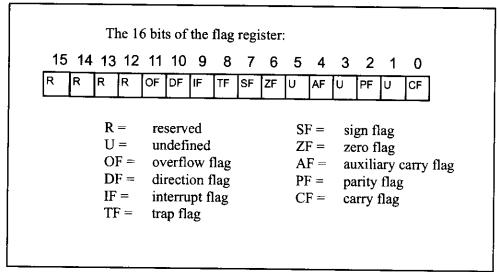

| Flag register 37                                         |    |

| Bits of the flag register 38                             |    |

| Flag register and ADD instruction 38                     |    |

|                                                          |    |

| Use of the zero flag for looping 40                      |    |

| SECTION 1.6. 9096 ADDRESSING MODES                       |    |

| SECTION 1.6: 80x86 ADDRESSING MODES 41                   |    |

| Register addressing mode 41                              |    |

| Immediate addressing mode 41                             |    |

| Direct addressing mode 42                                |    |

| Register indirect addressing mode 42                     |    |

| Based relative addressing mode 43                        |    |

| Indexed relative addressing mode 43                      |    |

| Based indexed addressing mode 44                         |    |

| Based indexed addressing mode 44                         |    |

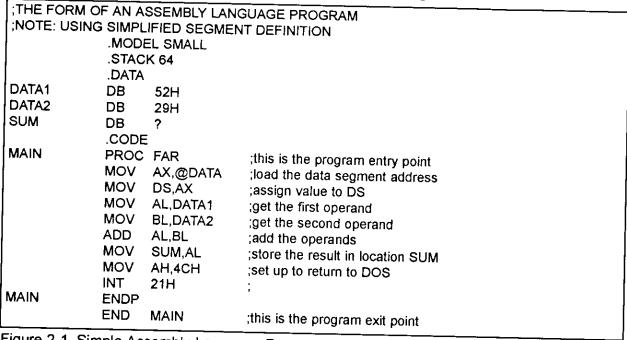

| SECTION 2.1: DIRECTIVES AND A SAMPLE PROGRAM 50 |

|-------------------------------------------------|

| Segments of a program 50                        |

| Stack segment definition 51                     |

| Data segment definition 51                      |

| Code segment definition 52                      |

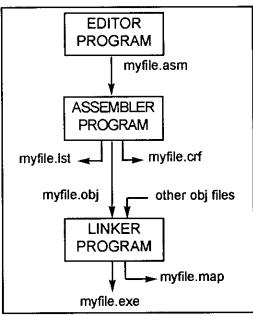

| SECTION 2.2: ASSEMBLE, LINK, AND RUN A PROGRAM  |

| .asm and .obj files 55                          |

| .lst file 55                                    |

| PAGE and TITLE directives 56                    |

| .crf file 56                                    |

| LINKing the program 57                          |

| .map file 57                                    |

| SECTION 2.3: MORE SAMPLE PROGRAMS 57            |

| Analysis of Program 2-1 58                      |

| Various approaches to Program 2-1 60            |

| Analysis of Program 2-2 62                      |

| Analysis of Program 2-3 62                      |

| Stack segment definition revisited 62           |

|                                                 |

| SECTION 2.4: CONTROL TRANSFER INSTRUCTIONS 64   |

| FAR and NEAR 64                                 |

| Conditional jumps 64                            |

| Short jumps 64                                  |

| Unconditional jumps 66                          |

| CALL statements 66                              |

| Assembly language subroutines 67                |

| Rules for names in Assembly language 67         |

| SECTION 2.5: DATA TYPES AND DATA DEFINITION 69  |

| 80x86 data types 69                             |

| Assembler data directives 69                    |

| ORG (origin) 69                                 |

| DB (define byte) 69                             |

| DUP (duplicate) 70                              |

| DW (define word) 70                             |

| EQU (equate) 71                                 |

| DD (define doubleword) 71                       |

| DQ (define quadword) 72                         |

| DT (define ten bytes) 72                        |

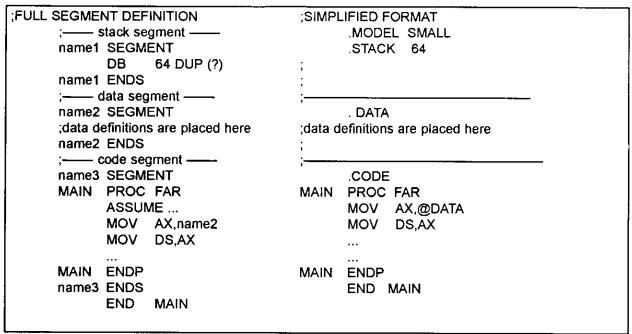

| SECTION 2.6: SIMPLIFIED SEGMENT DEFINITION 73   |

| 52011011 2.0. 51111 211 100                     |

|                                                 |

| Segment definition 74                           |

| Why COM files? 76                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------|

| Converting from EXE to COM 77                                                                                              |

| CHAPTER 3: ARITHMETIC AND LOGIC INSTRUCTIONS AND PROGRAMS 82                                                               |

| SECTION 3.1: UNSIGNED ADDITION AND SUBTRACTION 83                                                                          |

| Addition of unsigned numbers 83                                                                                            |

| CASE 1: Addition of individual byte and word data 83                                                                       |

| Analysis of Program 3-1a 84                                                                                                |

| CASE 2: Addition of multiword numbers 85                                                                                   |

| Analysis of Program 3-2 86                                                                                                 |

| Subtraction of unsigned numbers 87                                                                                         |

| SBB (subtract with borrow) 88                                                                                              |

| SECTION 3.2: UNSIGNED MULTIPLICATION AND DIVISION 88 Multiplication of unsigned numbers 88 Division of unsigned numbers 90 |

| SECTION 3.3: LOGIC INSTRUCTIONS AND SAMPLE PROGRAMS 93                                                                     |

| AND 93                                                                                                                     |

| OR 93                                                                                                                      |

| XOR 94                                                                                                                     |

| SHIFT 95                                                                                                                   |

| COMPARE of unsigned numbers 96                                                                                             |

| IBM BIOS method of converting from lowercase to uppercase 99                                                               |

| BIOS examples of logic instructions 100                                                                                    |

| SECTION 3.4 BCD AND ASCII OPERANDS AND INSTRUCTIONS 101                                                                    |

| BCD number system 101                                                                                                      |

| Unpacked BCD 102                                                                                                           |

| Packed BCD 102                                                                                                             |

| ASCII numbers 102                                                                                                          |

| ASCII to BCD conversion 102                                                                                                |

| ASCII to unpacked BCD conversion 102                                                                                       |

| ASCII to packed BCD conversion 103                                                                                         |

| Packed BCD to ASCII conversion 104                                                                                         |

| BCD addition and subtraction 104                                                                                           |

| BCD addition and correction 104                                                                                            |

| DAA 105                                                                                                                    |

| Summary of DAA action 105                                                                                                  |

| BCD subtraction and correction 105                                                                                         |

| Summary of DAS action 107                                                                                                  |

| ASCII addition and subtraction 109                                                                                         |

| Unpacked BCD multiplication and division 110                                                                               |

| AAD 110                                                                                                                    |

| AAD 110                                                                                                                    |

**SECTION 2.7: EXE VS. COM FILES**

76

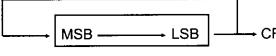

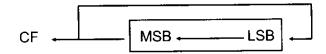

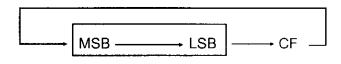

| SECTION 3.5: ROTATE INSTRUCTIONS 111  Rotating the bits of an operand right and left 111  ROR rotate right 111  ROL rotate left 112  RCR rotate right through carry 113  RCL rotate left through carry 113                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SECTION 3.6: BITWISE OPERATION IN THE C LANGUAGE  Bitwise operators in C 114  Bitwise shift operators in C 115  Packed BCD-to-ASCII conversion in C 116  Testing bits in C 116                                                                                                                                                                                                                                                                                                     |

| CHAPTER 4: BIOS AND DOS PROGRAMMING IN ASSEMBLY AND C 121                                                                                                                                                                                                                                                                                                                                                                                                                          |

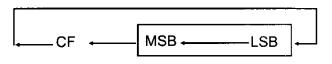

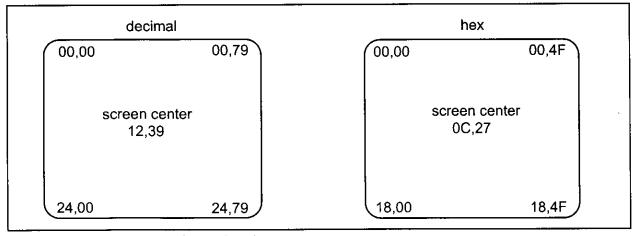

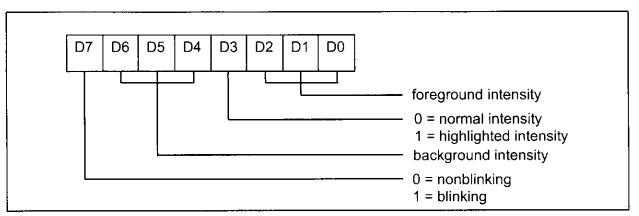

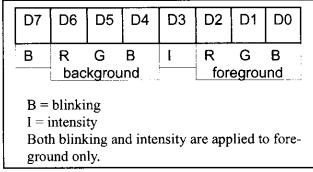

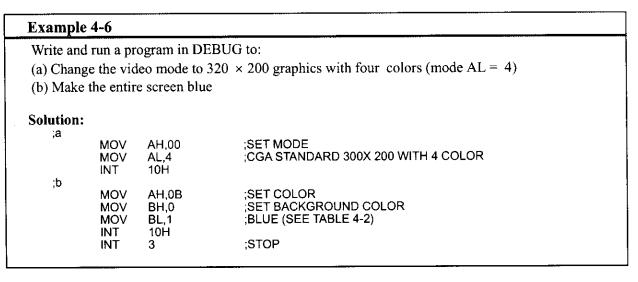

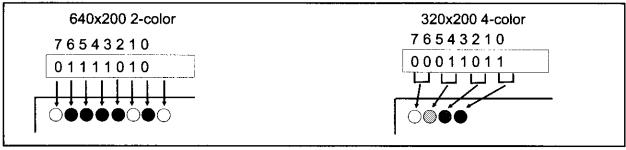

| Monitor screen in text mode 122 Clearing the screen using INT 10H function 06H 123 INT 10H function 02: setting the cursor to a specific location 123 INT 10H function 03: get current cursor position 124 Changing the video mode 124 Attribute byte in monochrome monitors 125 Attribute byte in CGA text mode 125 Graphics: pixel resolution and color 127 INT 10H and pixel programming 128                                                                                    |

| Drawing horizontal or vertical lines in graphics mode Changing the background color 129                                                                                                                                                                                                                                                                                                                                                                                            |

| SECTION 4.2: DOS INTERRUPT 21H 130  INT 21H option 09: outputting a string to the monitor 130  INT 21H option 02: outputting a character to the monitor 130  INT 21H option 01: inputting a character, with echo 130  INT 21H option 0AH: inputting a string from the keyboard 131  Inputting more than the buffer size 132  Use of carriage return and line feed 134  INT 21H option 07: keyboard input without echo 135  Using the LABEL directive to define a string buffer 136 |

| SECTION 4.3: INT 16H KEYBOARD PROGRAMMING  Checking a key press  139  Which key is pressed?  139                                                                                                                                                                                                                                                                                                                                                                                   |

| Programming BIOS interrupts with C/C++ 141 Programming INT 21H DOS functions calls with C/C++ 143 Accessing segment registers 144 Accessing the carry flag in int86 and intdos functions 144 Mixing C with Assembly and checking ZF 145 C function kbhit vs. INT 16H keyboard input 146                                                                                                                                                                                            |

|   | ~ | $\sim$ |

|---|---|--------|

| ı | ٦ | "      |

SECTION 5.1: WHAT IS A MACRO AND HOW IS IT USED? 151

|              | MACRO definition 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Comments in a macro 152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              | Analysis of Program 5-1 154                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              | LOCAL directive and its use in macros 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | INCLUDE directive 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | ON 5.2: MOUSE PROGRAMMING WITH INT 33H 161 INT 33H 161 Detecting the presence of a mouse 161 Some mouse terminology 162 Displaying and hiding the mouse cursor 162                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | Video resolution vs. mouse resolution in text mode 163 Video resolution vs. mouse resolution in graphics mode 163 Getting the current mouse cursor position (AX=03) 163 Setting the mouse pointer position (AX=04) 166 Getting mouse button press information (AX=05) 166 Monitoring and displaying the button press count program 167 Getting mouse button release information (AX=06) 168 Setting horizontal boundary for mouse pointer (AX=07) 168 Setting vertical boundary for mouse pointer (AX=08) 168 Setting an exclusion area for the mouse pointer (AX=10) 169 Getting mouse driver information (version) (AX=24H) 169 |

| CHAPTER 6: S | SIGNED NUMBERS, STRINGS, AND TABLES 173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SECTIO       | N 6.1: SIGNED NUMBER ARITHMETIC OPERATIONS 174                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| !<br>!<br>!  | Concept of signed numbers in computers 174 Signed byte operands 174 Positive numbers 174 Negative numbers 174 Word-sized signed numbers 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | When the overflow flag is set in 8-bit operations 176                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | Overflow flag in 16-bit operations 177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| )<br>]<br>2  | Avoiding erroneous results in signed number operations 178 IDIV (Signed number division) 179 IMUL (Signed number multiplication) 180 Arithmetic shift 182 SAR (shift arithmetic right) 182                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5            | SAL (shift arithmetic left) and SHL (shift left) 182                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Byte and word operands in string instructions DF, the direction flag DF, the direction flag 185 REP prefix 186 STOS and LODS instructions 186 Testing memory using STOSB and LODSB 187 The REPZ and REPNZ prefixes 187 SCAS (scan string) 189 Replacing the scanned character 189 XLAT instruction and look-up tables 190 Code conversion using XLAT 190  CHAPTER 7: MODULES; MODULAR AND C PROGRAMMING 193  SECTION 7.1: WRITING AND LINKING MODULES Why modules? 194 Writing modules 194 EXTRN directive 194 PUBLIC directive 194 END directive in modules 195 Linking modules together into one executable unit 196 SEGMENT directive 198 Complete stack segment definition 198 Complete data and code segment definitions 198 Analysis of Program 7-2 link map 200 Modular programming and the new segment definition 201  SECTION 7.2: SOME VERY USEFUL MODULES 203 Binary (hex)-to-ASCII conversion 204 Binary-to-ASCII module 205 ASCII-to-binary module 207 Calling module 207  SECTION 7.3: PASSING PARAMETERS AMONG MODULES Passing parameters via registers 208 Passing parameters via memory 208 Passing parameters via memory 208 Passing parameters via memory 208 Passing parameters via the stack 208 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

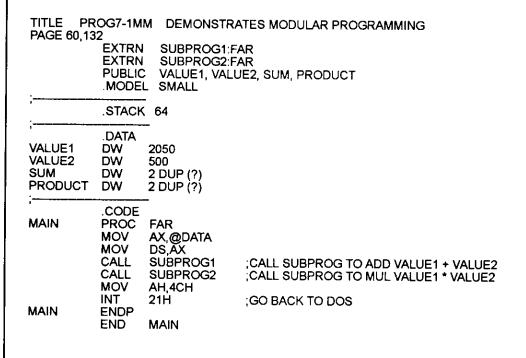

| Testing memory using STOSB and LODSB 187 The REPZ and REPNZ prefixes 187 SCAS (scan string) 189 Replacing the scanned character 189 XLAT instruction and look-up tables 190 Code conversion using XLAT 190  CHAPTER 7: MODULES; MODULAR AND C PROGRAMMING 193  SECTION 7.1: WRITING AND LINKING MODULES 194 Why modules? 194 Writing modules 194 EXTRN directive 194 PUBLIC directive 194 END directive in modules 195 Linking modules together into one executable unit 196 SEGMENT directive 198 Complete stack segment definition 198 Complete data and code segment definitions 198 Analysis of Program 7-2 link map 200 Modular programming and the new segment definition 201  SECTION 7.2: SOME VERY USEFUL MODULES 203 Binary (hex)-to-ASCII conversion 203 ASCII (decimal)-to-binary (hex) conversion 204 Binary-to-ASCII module 205 ASCII-to-binary module 207 Calling module 207  SECTION 7.3: PASSING PARAMETERS AMONG MODULES 208 Passing parameters via registers 208 Passing parameters via the stack 208                                                                                                                                                                                              |

| Replacing the scanned character 189 XLAT instruction and look-up tables 190 Code conversion using XLAT 190  CHAPTER 7: MODULES; MODULAR AND C PROGRAMMING 193  SECTION 7.1: WRITING AND LINKING MODULES 194 Why modules? 194 Writing modules 194 EXTRN directive 194 PUBLIC directive 194 END directive in modules 195 Linking modules together into one executable unit 196 SEGMENT directive 198 Complete stack segment definition 198 Complete data and code segment definitions 198 Analysis of Program 7-2 link map 200 Modular programming and the new segment definition 201  SECTION 7.2: SOME VERY USEFUL MODULES 203 Binary (hex)-to-ASCII conversion 203 ASCII (decimal)-to-binary (hex) conversion 204 Binary-to-ASCII module 205 ASCII-to-binary module 207 Calling module 207  SECTION 7.3: PASSING PARAMETERS AMONG MODULES 208 Passing parameters via registers 208 Passing parameters via the stack 208                                                                                                                                                                                                                                                                                              |

| SECTION 7.1: WRITING AND LINKING MODULES Why modules? 194 Writing modules 194 EXTRN directive 194 PUBLIC directive 194 END directive in modules 195 Linking modules together into one executable unit 196 SEGMENT directive 198 Complete stack segment definition 198 Complete data and code segment definitions 198 Analysis of Program 7-2 link map 200 Modular programming and the new segment definition 201  SECTION 7.2: SOME VERY USEFUL MODULES 203 Binary (hex)-to-ASCII conversion 203 ASCII (decimal)-to-binary (hex) conversion 204 Binary-to-ASCII module 205 ASCII-to-binary module 207 Calling module 207  SECTION 7.3: PASSING PARAMETERS AMONG MODULES 208 Passing parameters via memory 208 Passing parameters via the stack 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Why modules? 194 Writing modules 194 EXTRN directive 194 PUBLIC directive 194 END directive in modules 195 Linking modules together into one executable unit 196 SEGMENT directive 198 Complete stack segment definition 198 Complete data and code segment definitions 198 Analysis of Program 7-2 link map 200 Modular programming and the new segment definition 201  SECTION 7.2: SOME VERY USEFUL MODULES 203 Binary (hex)-to-ASCII conversion 203 ASCII (decimal)-to-binary (hex) conversion 204 Binary-to-ASCII module 205 ASCII-to-binary module 207 Calling module 207  SECTION 7.3: PASSING PARAMETERS AMONG MODULES 208 Passing parameters via registers 208 Passing parameters via memory 208 Passing parameters via the stack 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EXTRN directive 194 PUBLIC directive 194 END directive in modules 195 Linking modules together into one executable unit 196 SEGMENT directive 198 Complete stack segment definition 198 Complete data and code segment definitions 198 Analysis of Program 7-2 link map 200 Modular programming and the new segment definition 201  SECTION 7.2: SOME VERY USEFUL MODULES 203 Binary (hex)-to-ASCII conversion 203 ASCII (decimal)-to-binary (hex) conversion 204 Binary-to-ASCII module 205 ASCII-to-binary module 207 Calling module 207  SECTION 7.3: PASSING PARAMETERS AMONG MODULES 208 Passing parameters via registers 208 Passing parameters via memory 208 Passing parameters via the stack 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| END directive in modules 195 Linking modules together into one executable unit 196 SEGMENT directive 198 Complete stack segment definition 198 Complete data and code segment definitions 198 Analysis of Program 7-2 link map 200 Modular programming and the new segment definition 201  SECTION 7.2: SOME VERY USEFUL MODULES 203 Binary (hex)-to-ASCII conversion 203 ASCII (decimal)-to-binary (hex) conversion 204 Binary-to-ASCII module 205 ASCII-to-binary module 207 Calling module 207  SECTION 7.3: PASSING PARAMETERS AMONG MODULES 208 Passing parameters via registers 208 Passing parameters via memory 208 Passing parameters via the stack 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SEGMENT directive 198 Complete stack segment definition 198 Complete data and code segment definitions 198 Analysis of Program 7-2 link map 200 Modular programming and the new segment definition 201  SECTION 7.2: SOME VERY USEFUL MODULES 203 Binary (hex)-to-ASCII conversion 203 ASCII (decimal)-to-binary (hex) conversion 204 Binary-to-ASCII module 205 ASCII-to-binary module 207 Calling module 207  SECTION 7.3: PASSING PARAMETERS AMONG MODULES 208 Passing parameters via registers 208 Passing parameters via memory 208 Passing parameters via the stack 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Analysis of Program 7-2 link map 200 Modular programming and the new segment definition 201  SECTION 7.2: SOME VERY USEFUL MODULES 203 Binary (hex)-to-ASCII conversion 203 ASCII (decimal)-to-binary (hex) conversion 204 Binary-to-ASCII module 205 ASCII-to-binary module 207 Calling module 207  SECTION 7.3: PASSING PARAMETERS AMONG MODULES 208 Passing parameters via registers 208 Passing parameters via memory 208 Passing parameters via the stack 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Binary (hex)-to-ASCII conversion 203 ASCII (decimal)-to-binary (hex) conversion 204 Binary-to-ASCII module 205 ASCII-to-binary module 207 Calling module 207  SECTION 7.3: PASSING PARAMETERS AMONG MODULES 208 Passing parameters via registers 208 Passing parameters via memory 208 Passing parameters via the stack 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ASCII (decimal)-to-binary (hex) conversion 204 Binary-to-ASCII module 205 ASCII-to-binary module 207 Calling module 207  SECTION 7.3: PASSING PARAMETERS AMONG MODULES 208 Passing parameters via registers 208 Passing parameters via memory 208 Passing parameters via the stack 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Passing parameters via registers 208 Passing parameters via memory 208 Passing parameters via the stack 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Passing parameters via memory 208 Passing parameters via the stack 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SECTION 7.4. COMBINING ASSEMBLY LANGUAGE AND C. 210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SECTION 7.4: COMBINING ASSEMBLY LANGUAGE AND C 210<br>Why C? 210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Inserting 80x86 assembly code into C programs 211 C programs that call Assembly procedures 212 C calling convention 213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| How parameters are returned to C 214 New assemblers and linking with C 215                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Passing array addresses from C to the stack Linking assembly language routines with C 217                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CHAPTER S | R: 32-BIT | 'PROGR | AMMING | FOR 386 | AND 4 | 186 MACHINES | -220 |

|-----------|-----------|--------|--------|---------|-------|--------------|------|

|-----------|-----------|--------|--------|---------|-------|--------------|------|

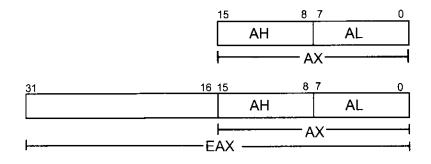

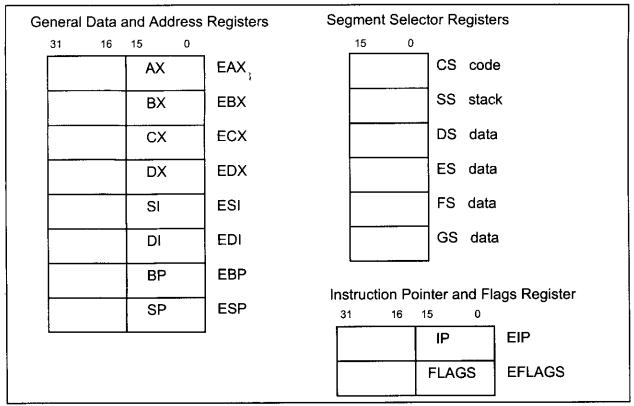

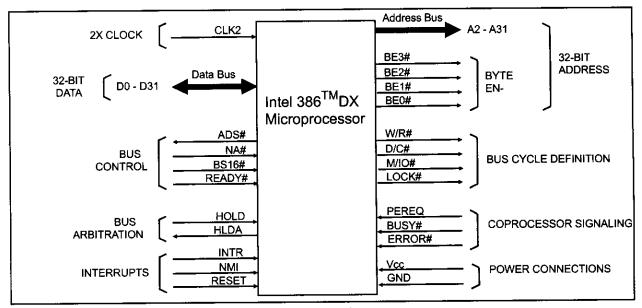

| SECTION 8.1: 80380/80480 IV               |                                         |                  | 221<br>222     |

|-------------------------------------------|-----------------------------------------|------------------|----------------|

| General registers are p                   |                                         |                  |                |

| 386/486 maximum me                        |                                         |                  |                |

| Accessing 32-bit regist                   |                                         |                  | assemblers 224 |

| Little endian revisited                   | 226                                     | 1                |                |

| SECTION 8.2: SOME SIMPLE                  | E 386/48                                | 6 PROGRAMS       | 226            |

| Adding 16-bit words u                     |                                         |                  | 226            |

| Adding multiword data                     |                                         |                  | 228            |

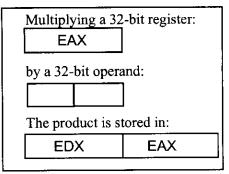

| Multiplying a 32-bit of                   |                                         |                  |                |

| 32-bit by 16-bit multip                   |                                         | -                |                |

| 32 on 6, 10 on man.p                      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                  | 8              |

| SECTION 8.3: 80x86 PERFO                  | RMANC!                                  | E COMPARISO      | N 231          |

| Running an 8086 prog                      | ram acros                               | ss the 80x86 far | nily 231       |

|                                           |                                         |                  |                |

|                                           |                                         |                  |                |

| CHAPTER 9: 8088, 80286 MICROPR            | OCESSO                                  | DES AND ISA      | BUS 235        |

| CHAPTER 9: 6006, 60280 MICROFR            | .OCESSC                                 | JRS AND ISA      | 503 233        |

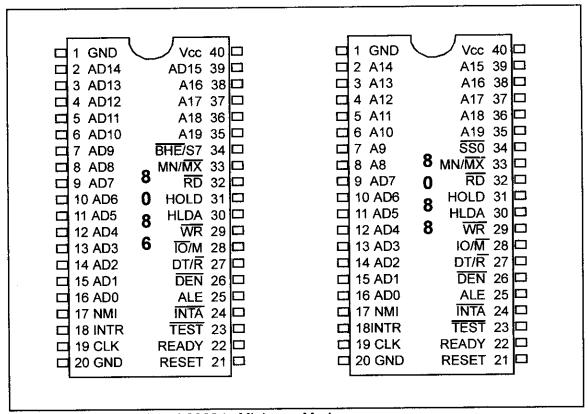

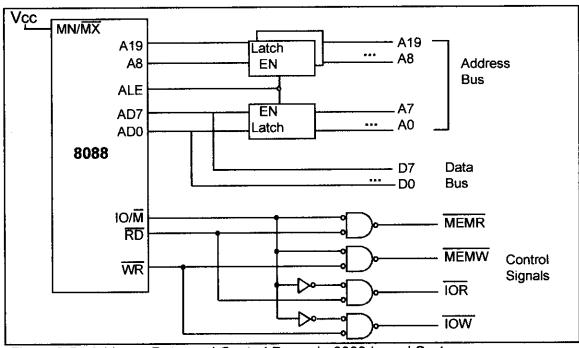

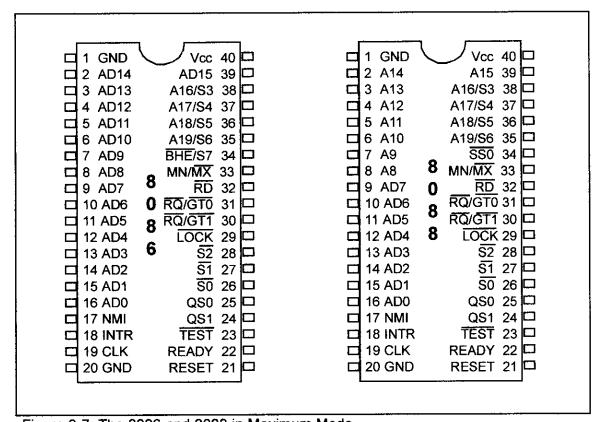

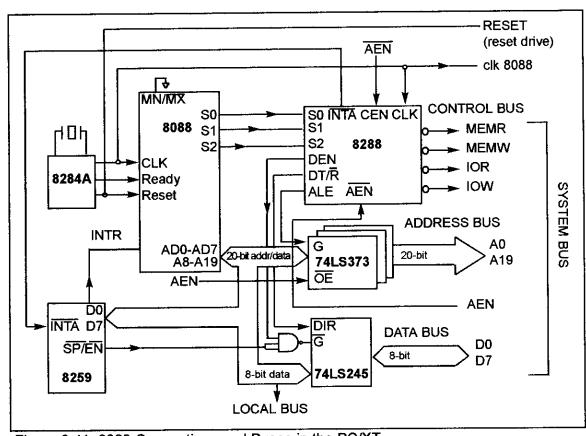

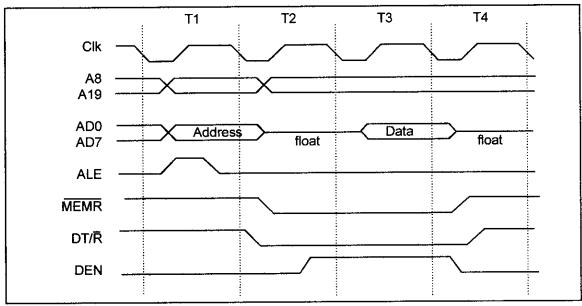

| SECTION 9.1: 8088 MICROI                  | PROCES                                  | SOR 236          |                |

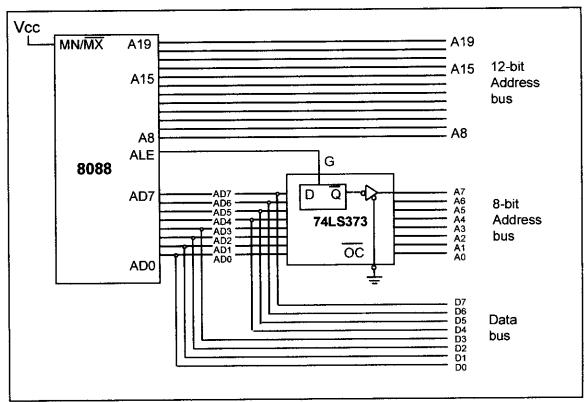

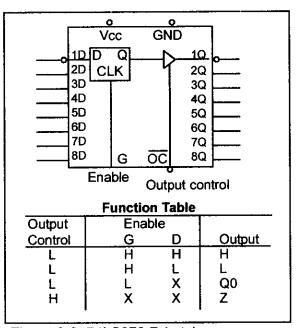

| Microprocessor buses                      | 236                                     |                  |                |

| Data bus in 8088 23                       |                                         |                  |                |

| Address bus in 8088                       | 238                                     |                  |                |

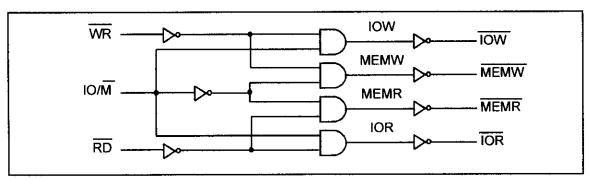

| 8088 control bus                          | 238                                     |                  |                |

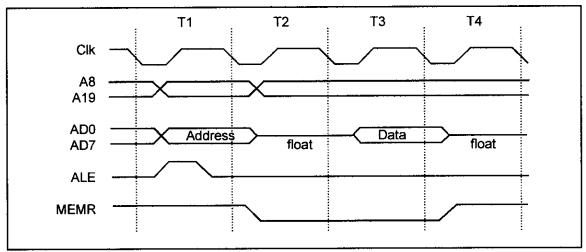

| Bus timing of 8088                        | 239                                     |                  |                |

| Other 8088 pins                           | 240                                     |                  |                |

|                                           |                                         |                  |                |

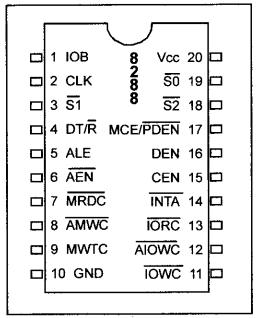

| SECTION 9.2: 8284 AND 82                  |                                         | ORTING CHIP      | S 242          |

| 8288 bus controller                       | 242                                     |                  |                |

| Input signals 242                         |                                         |                  |                |

| Output signals 243                        |                                         |                  |                |

| 8284 clock generator                      | 244                                     |                  |                |

| Input pins 244                            |                                         |                  |                |

| Output signals 245                        |                                         |                  |                |

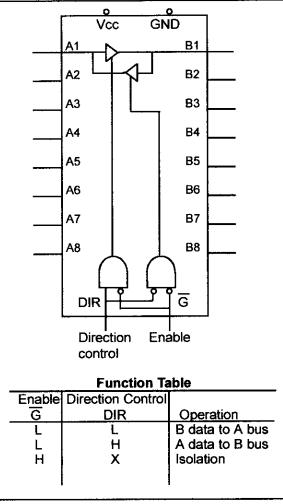

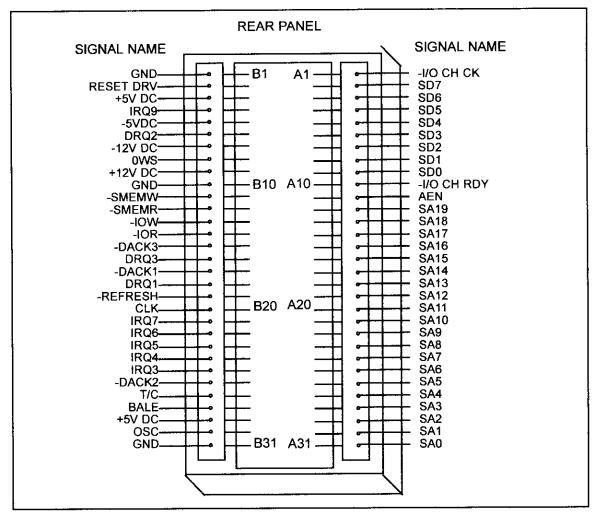

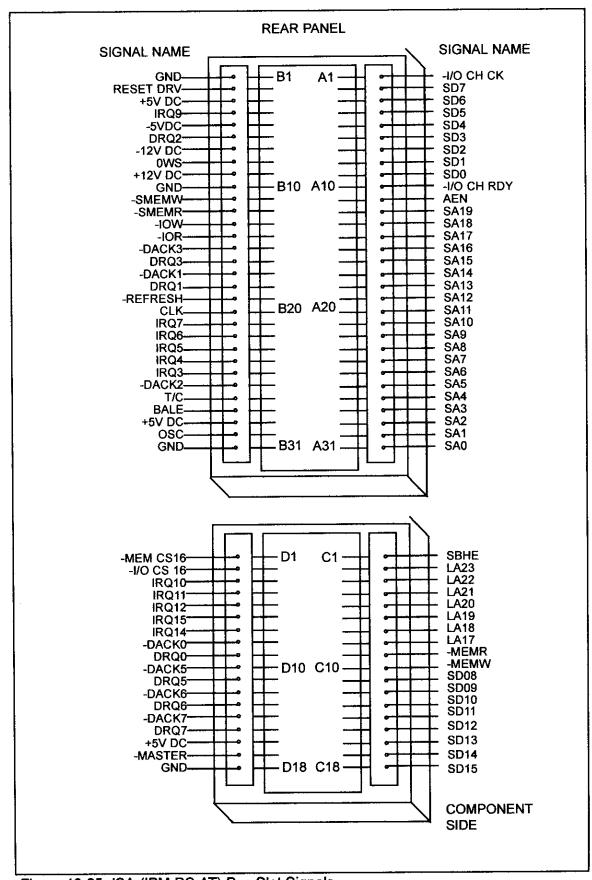

| SECTION 9.3: 8-BIT SECTIO                 | M OF IS                                 | A RUS 2/18       |                |

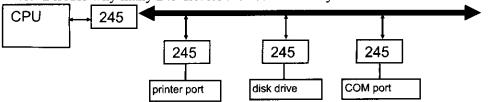

| A bit of bus history                      | 246                                     | A DOS 240        |                |

|                                           |                                         | 247              |                |

| Local bus vs. system b<br>Address bus 247 | Jus                                     | 247              |                |

| Data bus 248                              |                                         |                  |                |

| Control bus 249                           |                                         |                  |                |

|                                           | 249                                     |                  |                |

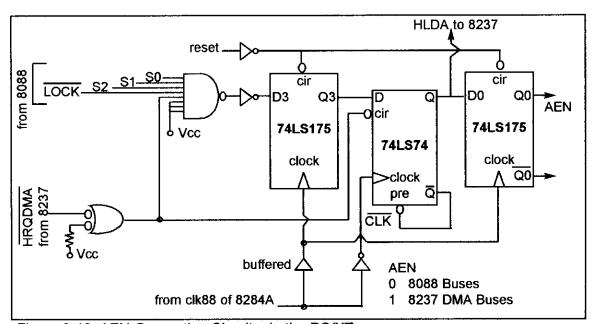

| One bus, two masters                      |                                         |                  |                |

| AEN signal generation                     |                                         | 250              |                |

| Control of the bus by I                   | DIVIA                                   | 250              |                |

| Bus boosting 250                          | A L                                     | 250              |                |

| 8-bit section of the ISA                  | A DUS                                   | 250              |                |

|                                           |                                         |                  |                |

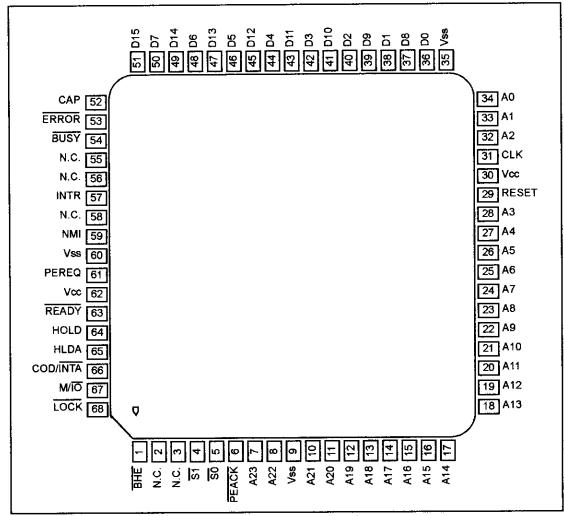

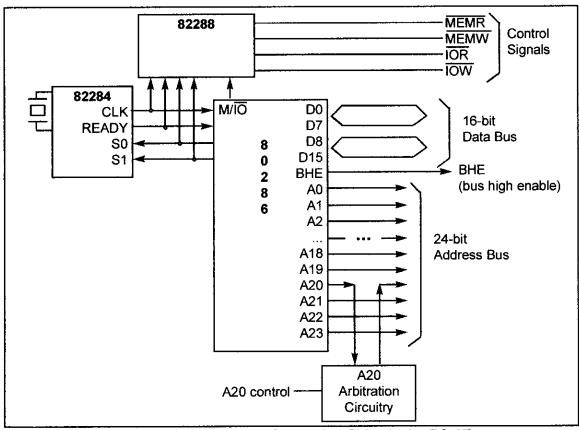

| SECTION 9.4: 80286 MIC | CROPROCESSOR | 251 |

|------------------------|--------------|-----|

| Pin descriptions       | 252          |     |

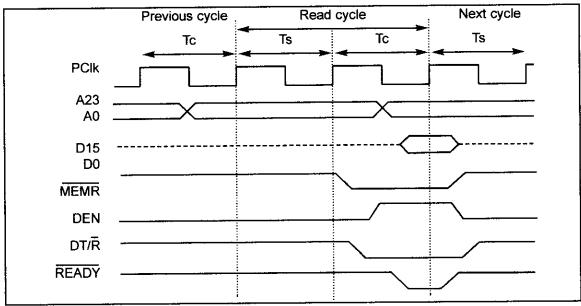

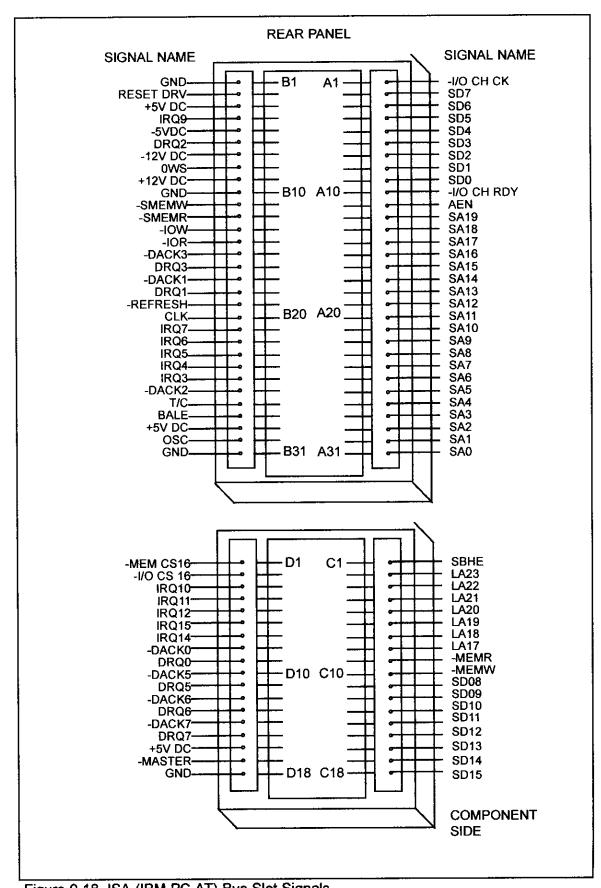

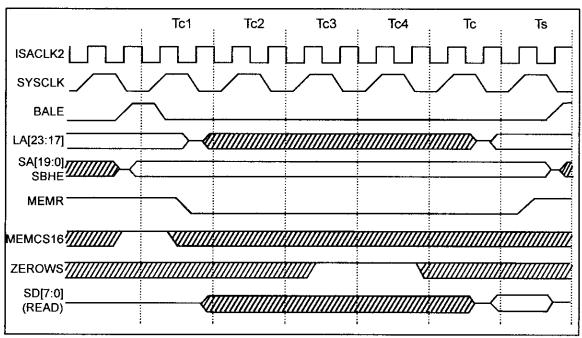

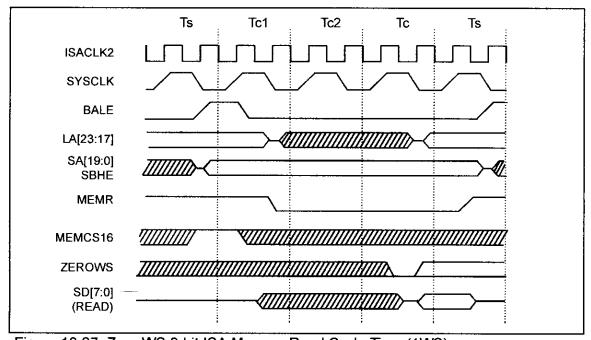

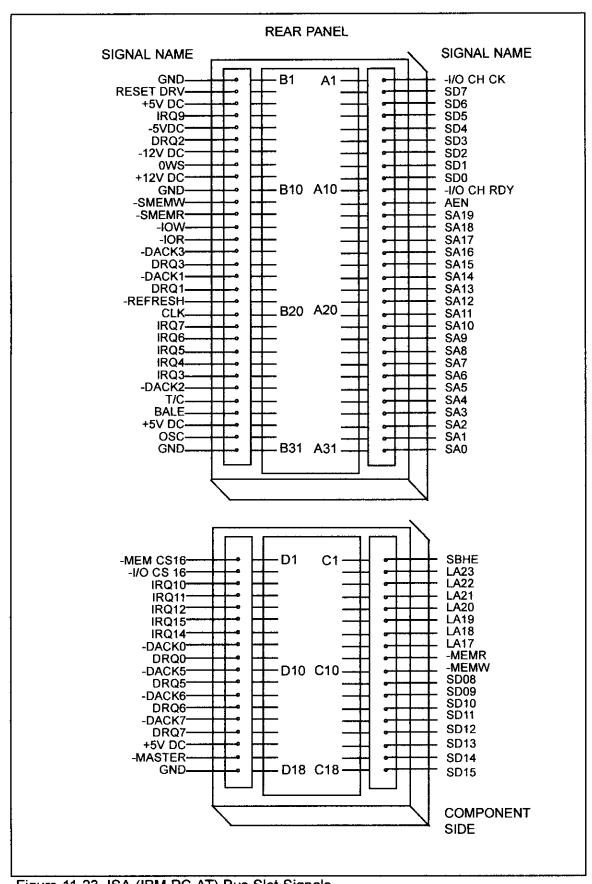

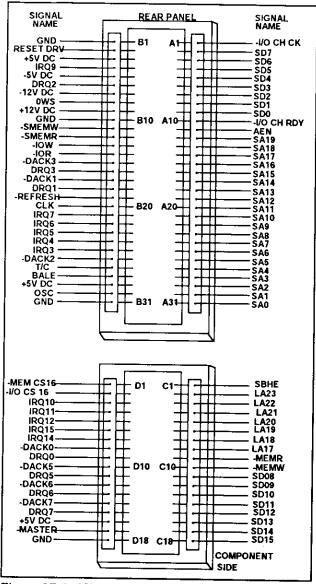

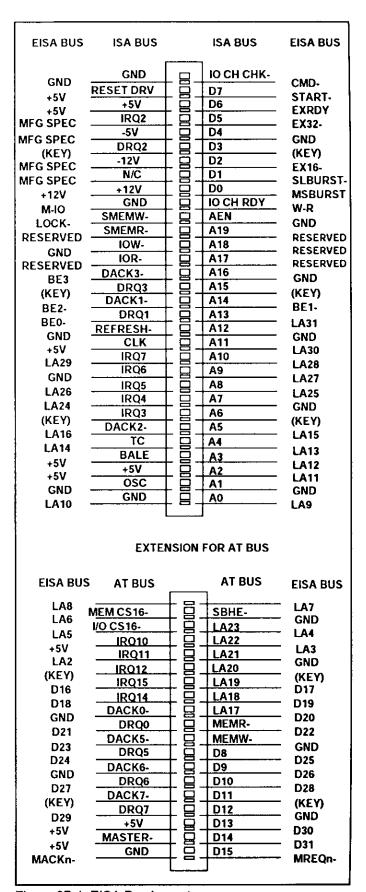

SECTION 9.5: 16-BIT ISA BUS

Exploring ISA bus signals 255

Address bus 256 Data bus 256

Memory and I/O control signals 256

Other control signals

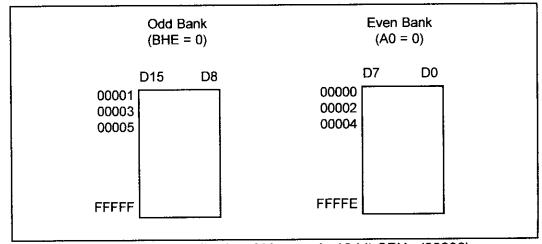

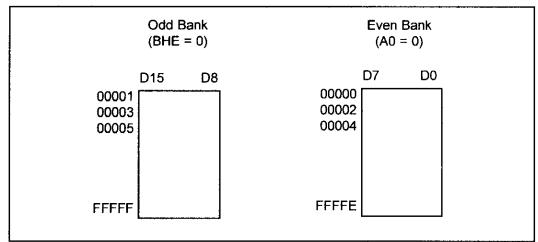

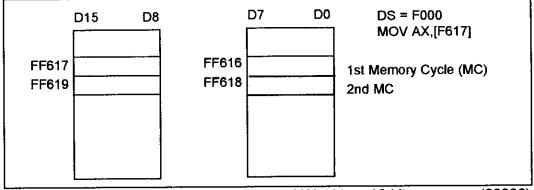

ODD and EVEN bytes and BHE

259

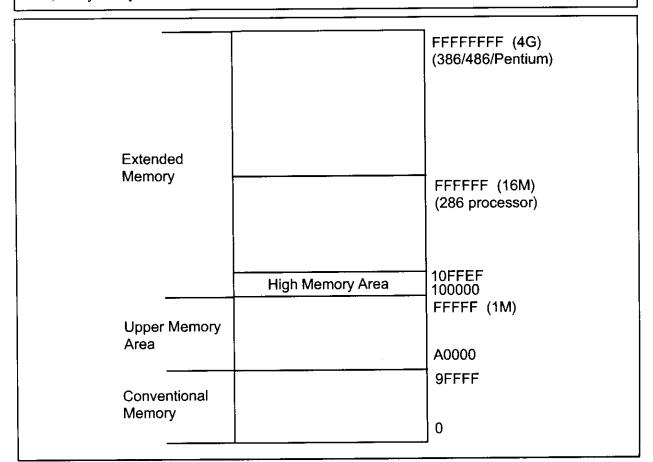

A20 gate and the case of high memory area (HMA) 260

255

#### CHAPTER 10: MEMORY AND MEMORY INTERFACING 265

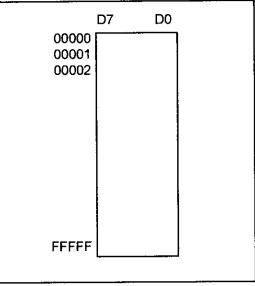

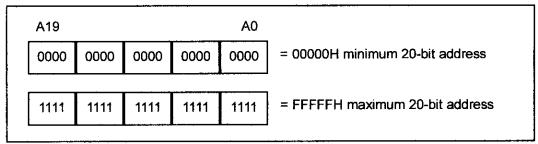

## SECTION 10.1: SEMICONDUCTOR MEMORY FUNDAMENTALS 266

Memory capacity 266

266 Memory organization

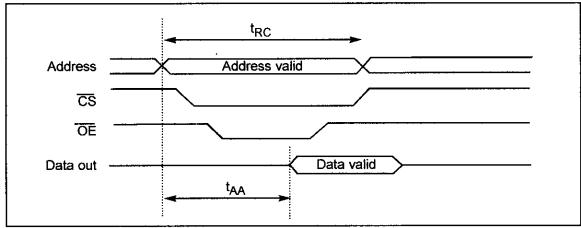

Speed 267

ROM (read-only memory) 267

PROM (programmable ROM) or OTP ROM 268

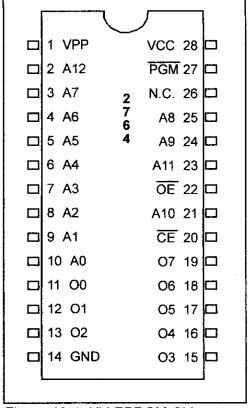

EPROM (erasable programmable ROM) 268

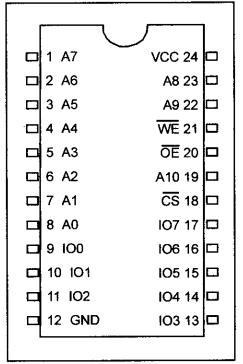

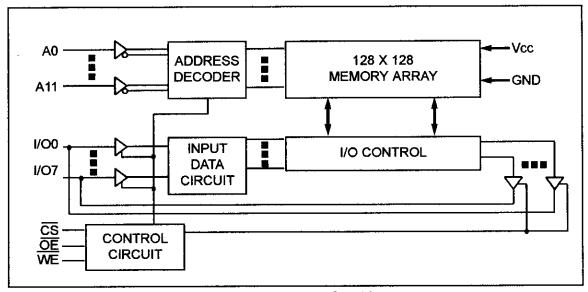

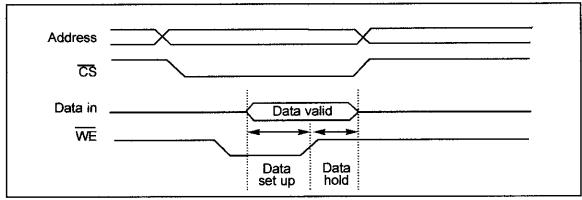

EEPROM (electrically erasable programmable ROM) 269

Flash memory 270

Mask ROM 271

RAM (random access memory)

SRAM (static RAM) 271

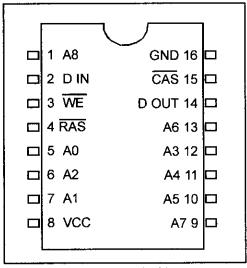

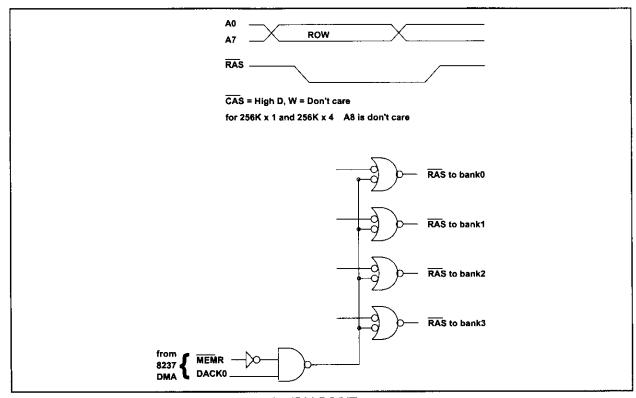

DRAM (dynamic RAM) 273

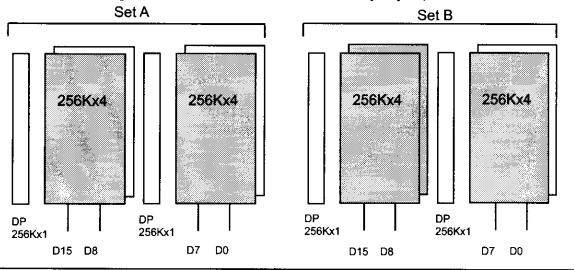

Packaging issue in DRAM 273

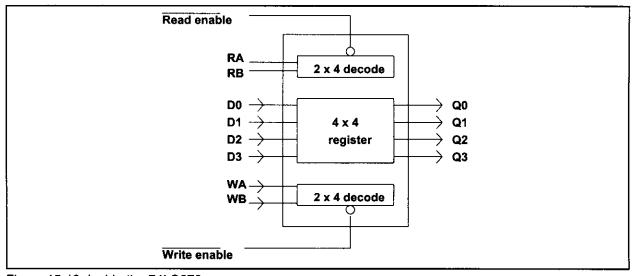

DRAM, SRAM and ROM organizations 275

NV-RAM (nonvolatile RAM) 276

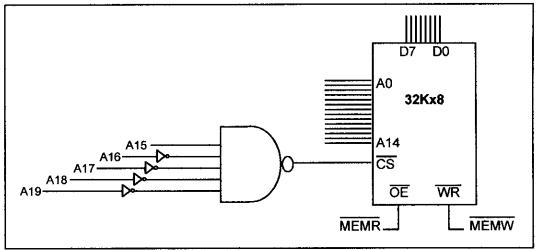

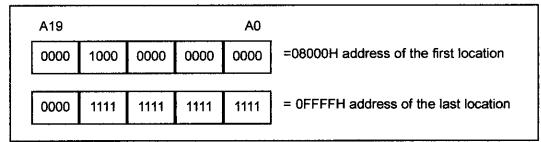

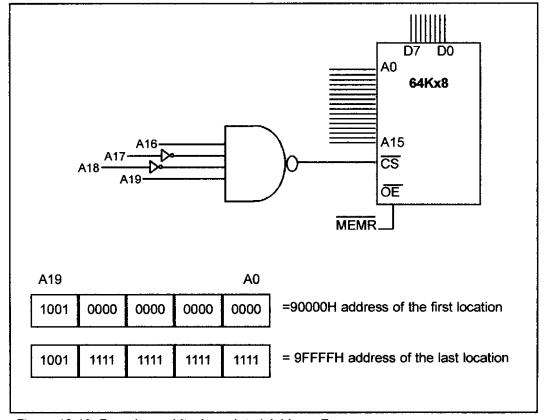

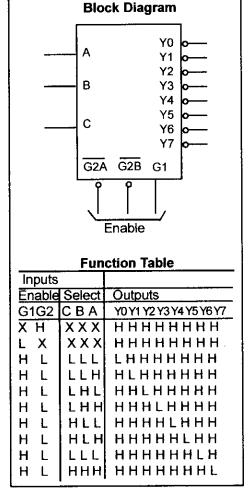

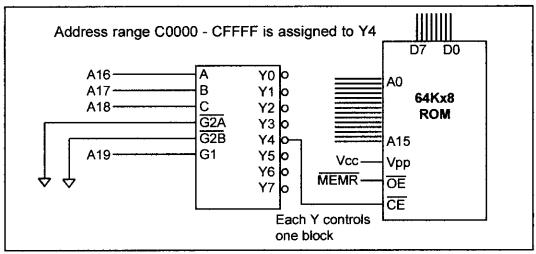

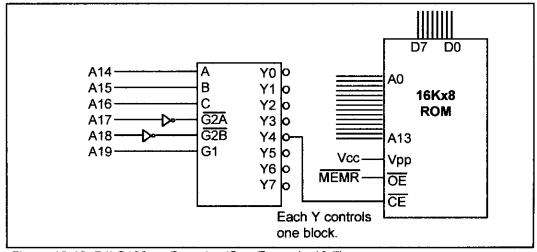

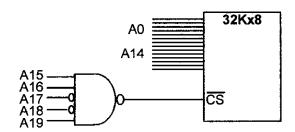

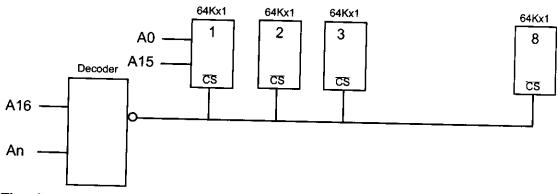

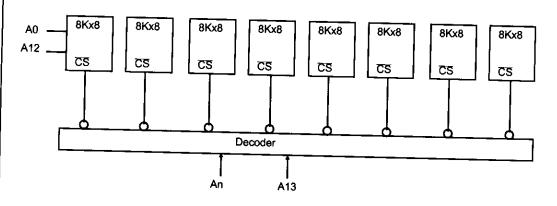

#### SECTION 10.2: MEMORY ADDRESS DECODING 276

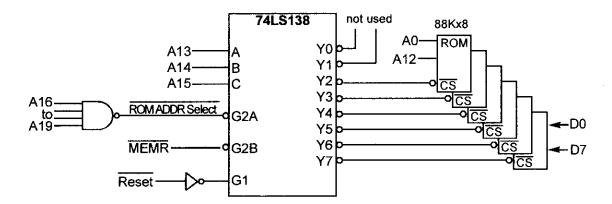

Simple logic gate as address decoder Using the 74LS138 as decoder

278

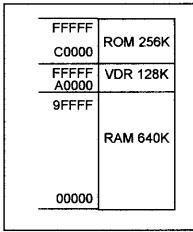

## SECTION 10.3: IBM PC MEMORY MAP 280

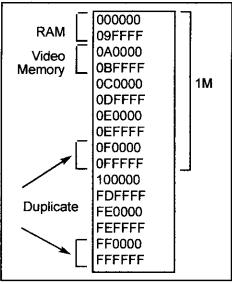

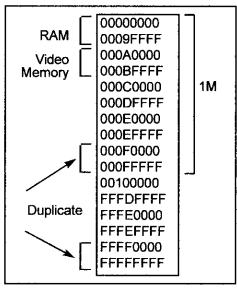

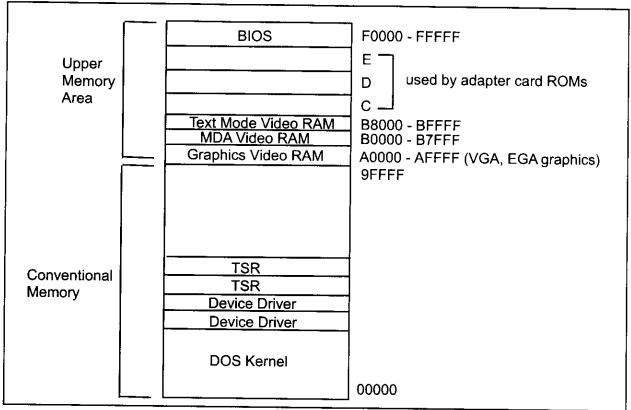

Conventional memory: 640K of RAM 281

BIOS data area

282

Video display RAM (VDR) map 282

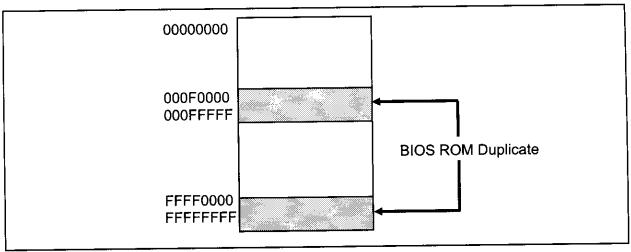

ROM address and cold boot on the PC 283

## SECTION 10.4: DATA INTEGRITY IN RAM AND ROM

284

Checksum byte Checksum program

286

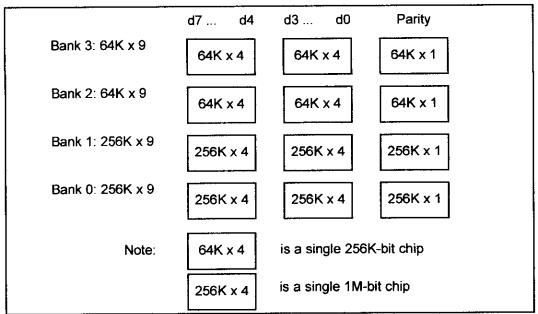

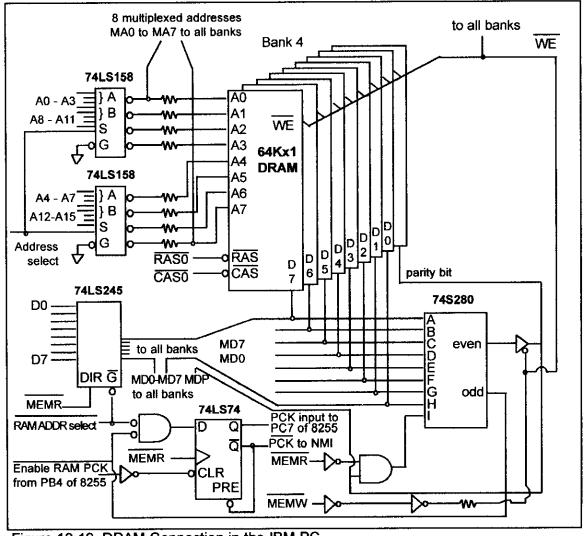

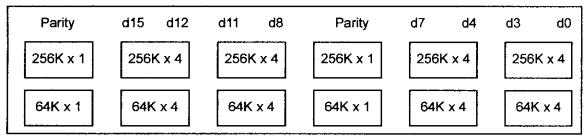

Use of parity bit in DRAM error detection

DRAM memory banks

Parity bit generator/checker in the IBM PC

74S280 parity bit generator and checker 288

284

286

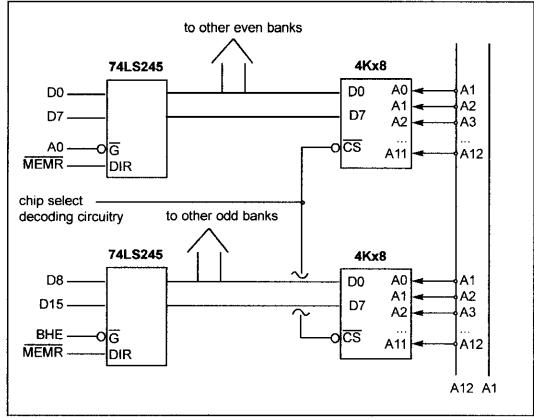

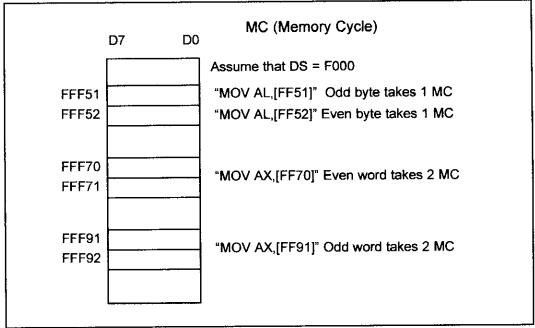

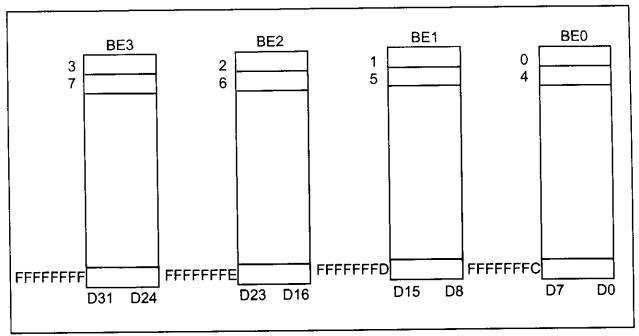

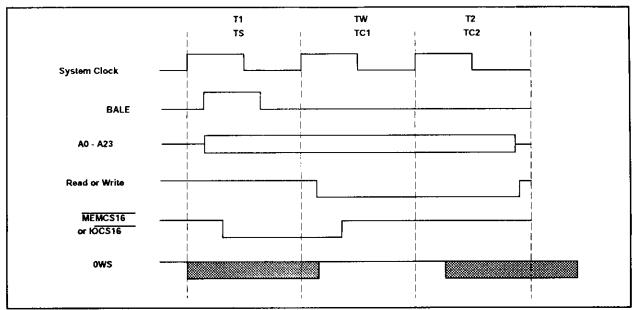

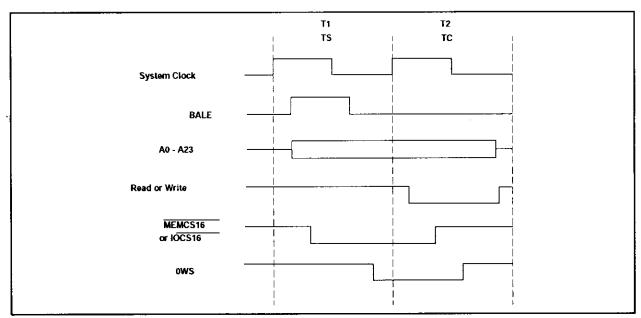

| Memory cycle time and inserting wait states 291 Accessing EVEN and ODD words 292 Bus bandwidth 293                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

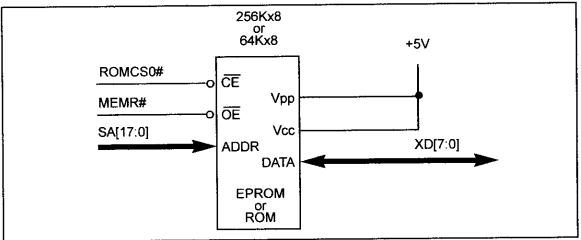

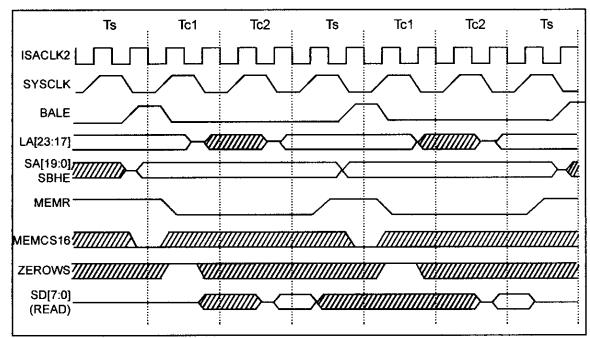

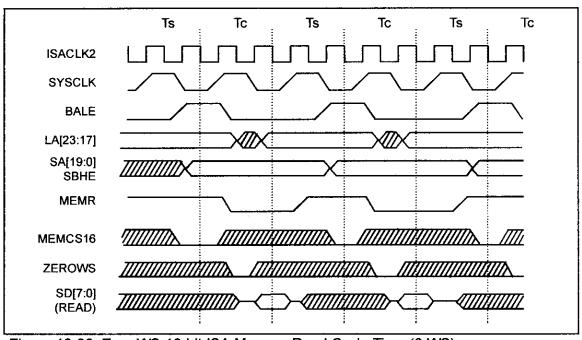

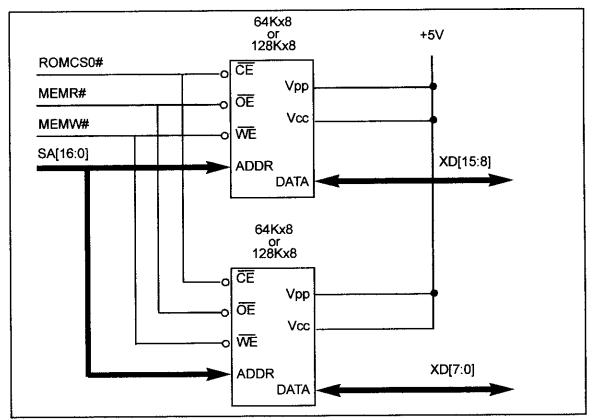

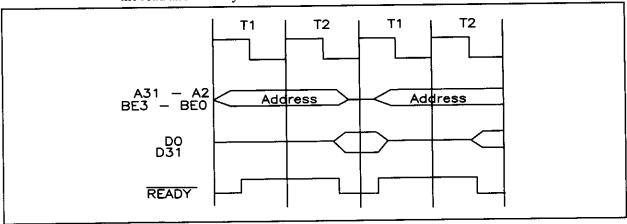

| SECTION 10.6: ISA BUS MEMORY INTERFACING 295 Address bus signals 295 Memory control signals 295 ISA bus timing for memory 299 8-bit memory timing for ISA bus 299                                                                                                                                                                        |

| ROM duplicate and x86 PC memory map Shadow RAM 302 DIMM and SIMM memory modules 302                                                                                                                                                                                                                                                      |

| CHAPTER 11: I/O AND THE 8255; ISA BUS INTERFACING 309                                                                                                                                                                                                                                                                                    |

| SECTION 11.1: 8088 INPUT/OUTPUT INSTRUCTIONS 310 8-bit data ports 310 How to use I/O instructions 311                                                                                                                                                                                                                                    |

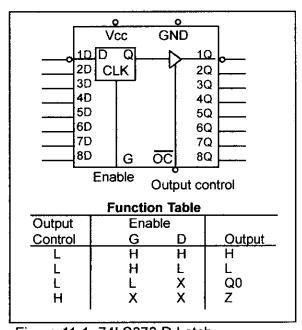

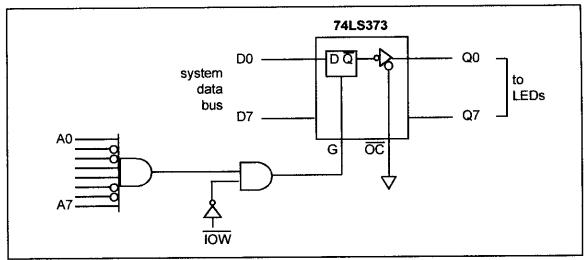

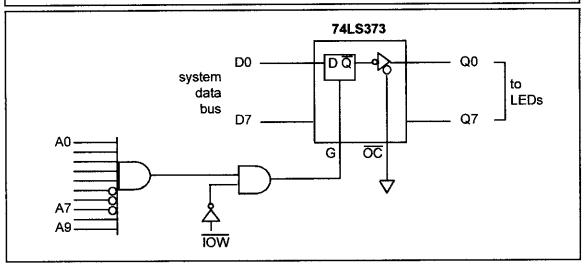

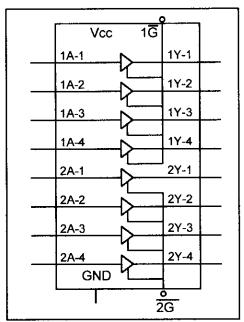

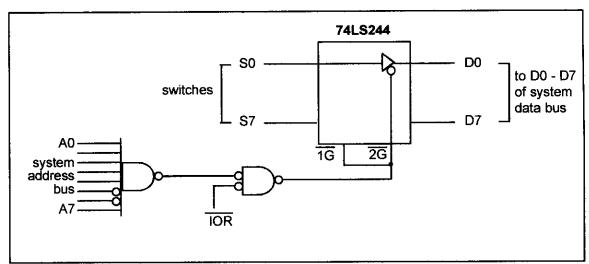

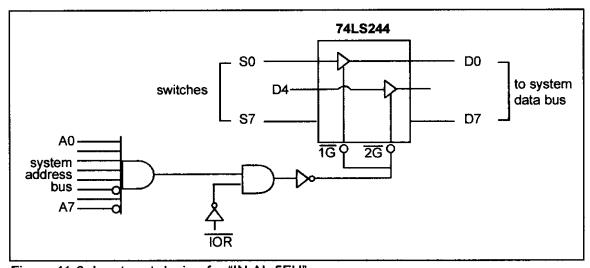

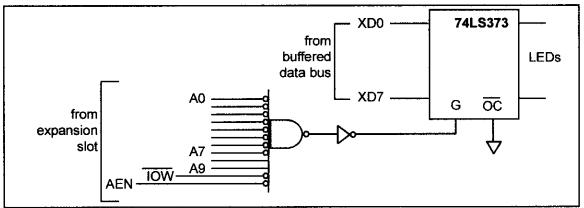

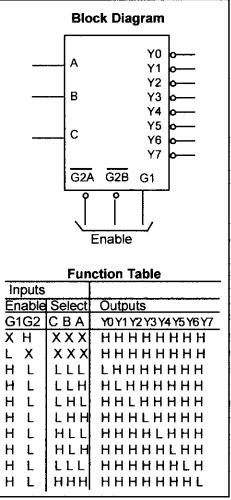

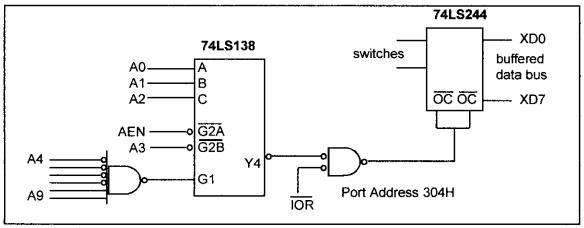

| SECTION 10.2: I/O ADDRESS DECODING AND DESIGN 312 Using the 74LS373 in an output port design 312 IN port design using the 74LS244 312 Memory map I/O 314                                                                                                                                                                                 |

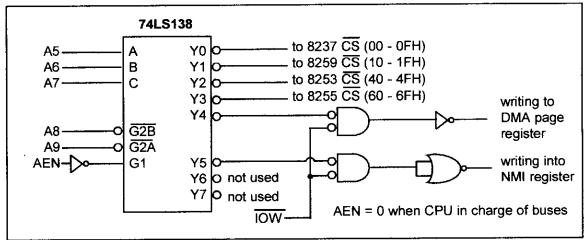

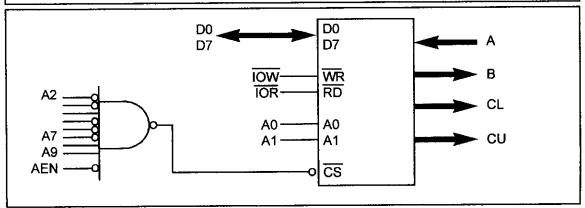

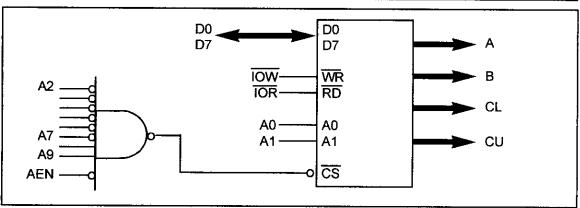

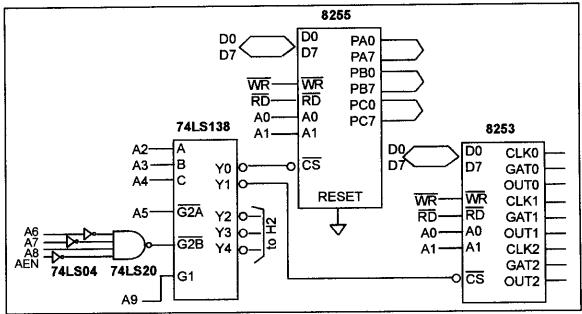

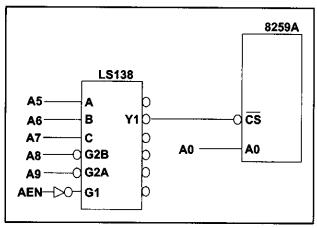

| SECTION 11.3: I/O ADDRESS MAP OF X86 PCS 316 Absolute vs. linear select address decoding 316 Prototype addresses 300 - 31FH in the x86 PC 316 Use of simple logic gates as address decoders 316 Use of 74LS138 as decoder 318 IBM PC I/O address decoder 318 Use of the 8255 in the IBM PC/XT 341 Port 61H and time delay generation 319 |

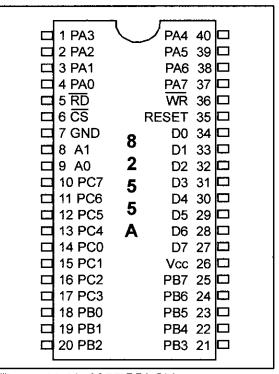

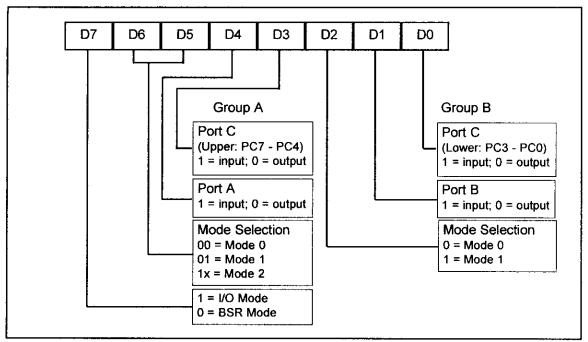

| SECTION 11.4: 8255 PPI CHIP 320 Mode selection of the 8255A 321                                                                                                                                                                                                                                                                          |

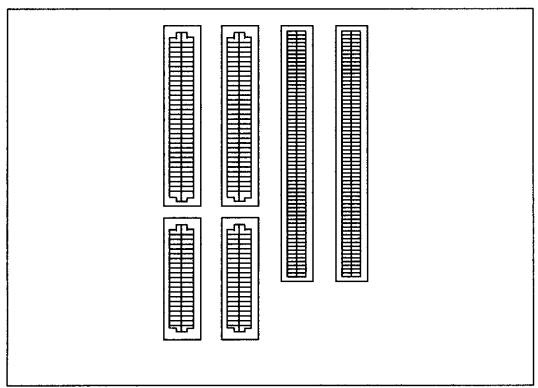

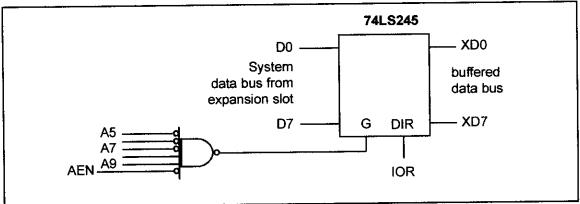

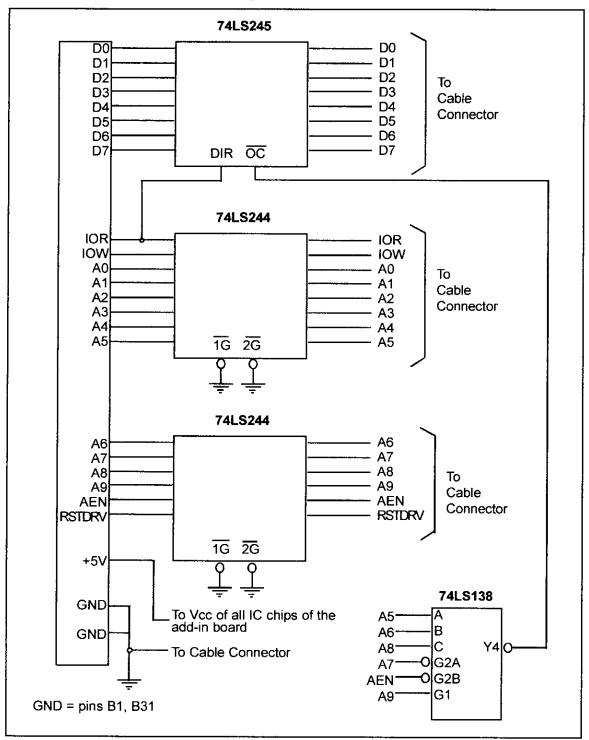

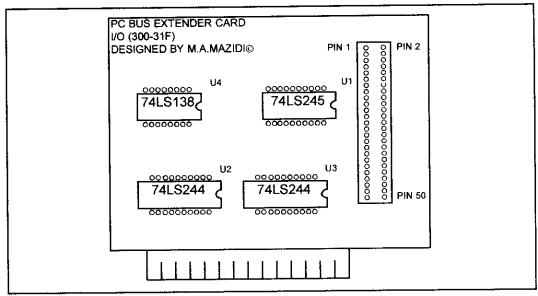

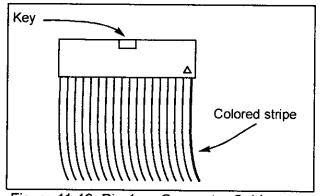

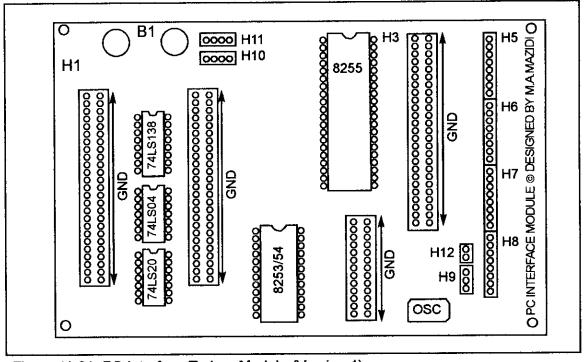

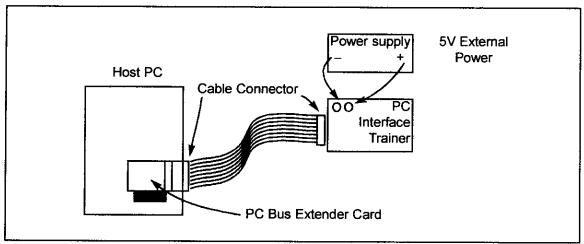

| SECTION 11.5: PC INTERFACE TRAINER AND BUS EXTENDER 325 PC I/O Bus Extender 325 Buffering 300 - 31F address range 326                                                                                                                                                                                                                    |

| Installing the PC Bus Extender and booting the PC Failure to boot 327 PC Interface Trainer 327 Design of the PC Trainer 328 The role of H1 and H2 328                                                                                                                                                                                    |

| Connecting the Module Trainer to the PC and testing 328 Testing the 8255 port 329 Testing Port A 330                                                                                                                                                                                                                                     |

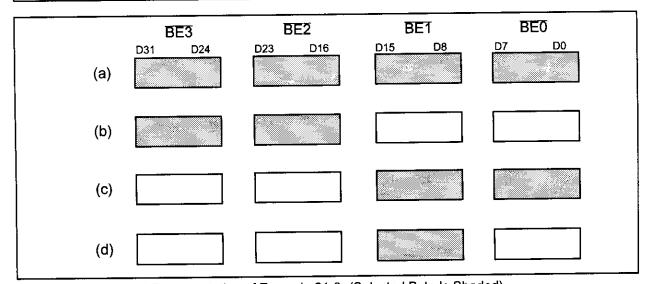

SECTION 10.5: 16-BIT MEMORY INTERFACING

ODD and EVEN banks 289

289

| Visual C/C++ I/O programming 332  Visual C++ output example 332  Visual C++ input example 332  I/O programming in Turbo C/C++ 334  I/O programming in Linux C/C++ 335                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Linux C/C++ program with I/O functions 335                                                                                                                                                                                                                                                                                                                                                      |

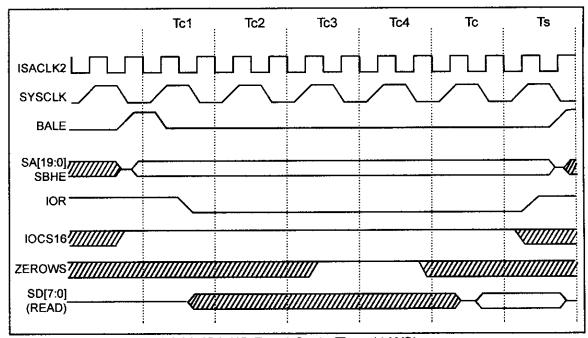

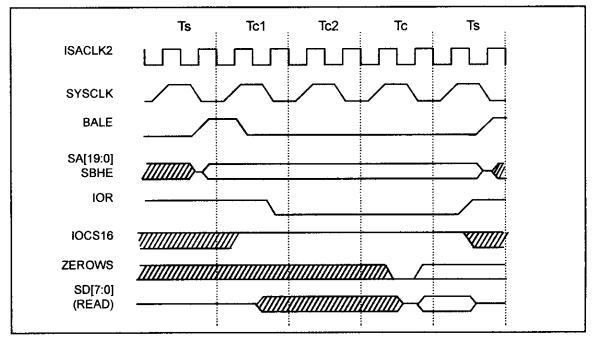

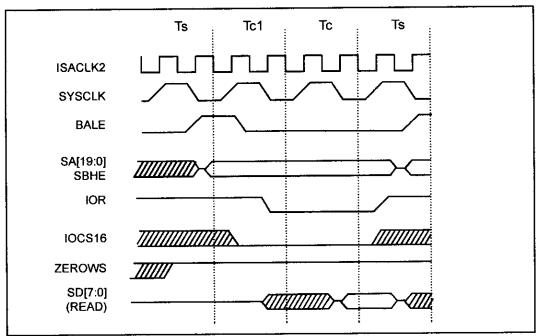

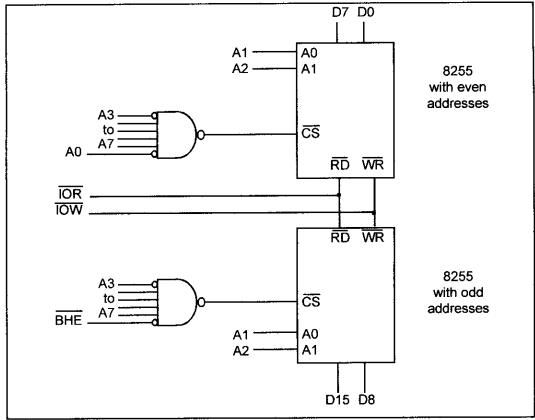

| SECTION 11.7: 8-BIT AND 16-BIT I/O TIMING IN ISA BUS  8-bit and 16-bit I/O in ISA bus 338  I/O signals of the ISA bus 339  8-bit timing and operation in ISA bus 341  16-bit I/O operation and timing in ISA bus 342  16-bit data ports instruction 342  16-bit I/O timing and operation via ISA bus 342  I/O bus bandwidth for ISA 343  Interfacing 8-bit peripherals to a 16-bit data bus 344 |

| CHAPTER 12: INTERFACING TO THE PC: LCD, MOTOR, ADC, AND SENSOR 351                                                                                                                                                                                                                                                                                                                              |

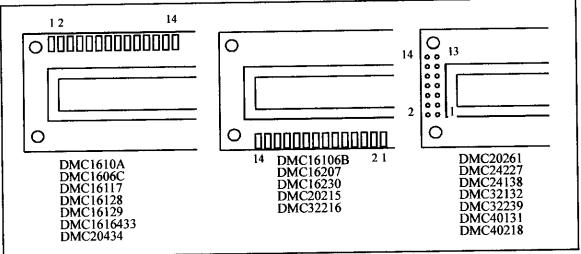

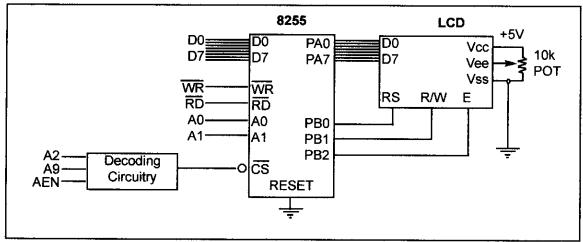

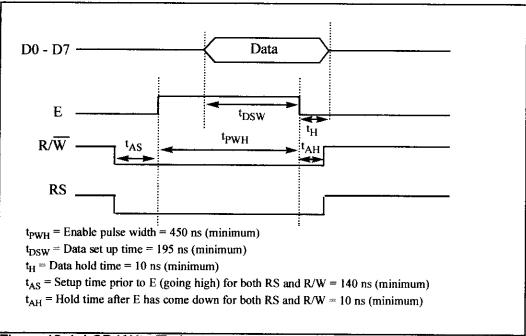

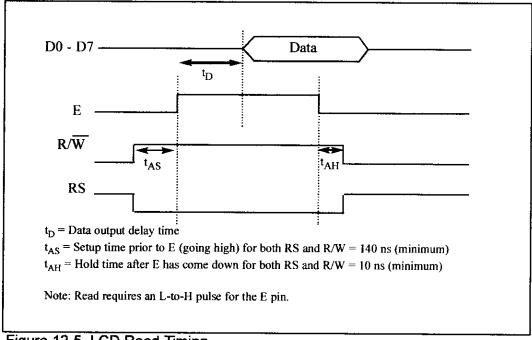

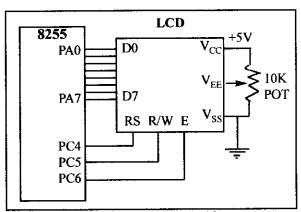

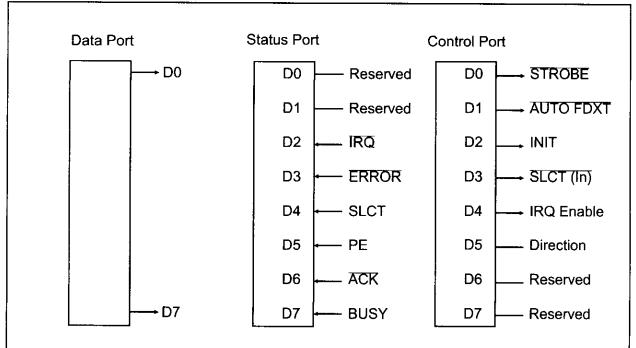

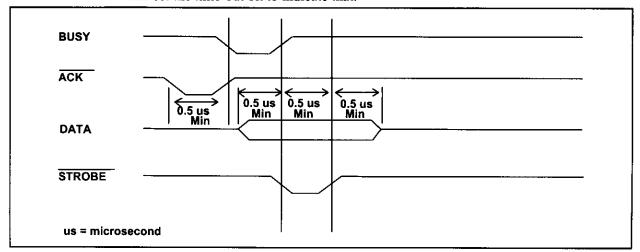

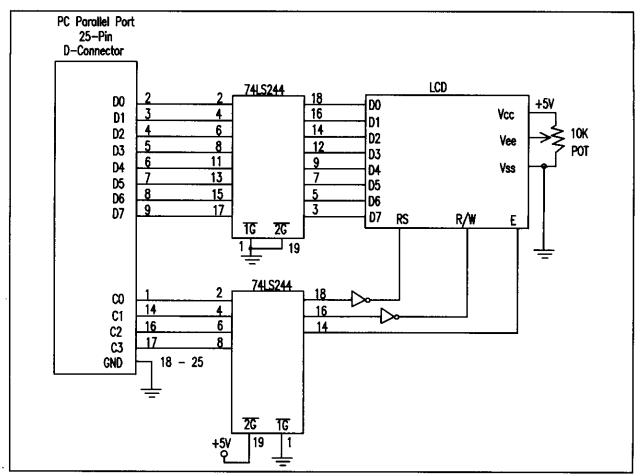

| SECTION 12.1: INTERFACING AN LCD TO THE PC  LCD operation 352  LCD pin descriptions 352  Sending commands to LCDs 353  Sending data to the LCD 355  Checking LCD busy flag 356  LCD cursor position 357  LCD programming in Visual C/C++ 358  LCD timing and data sheet 358                                                                                                                     |

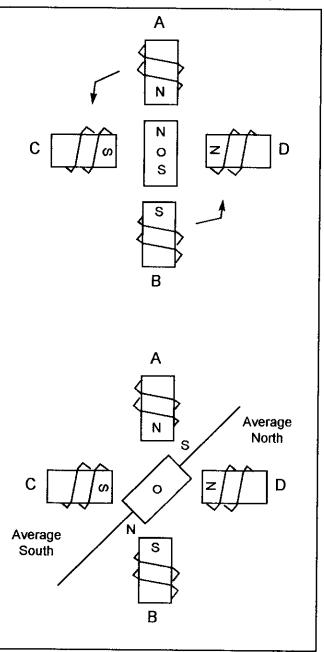

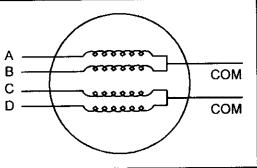

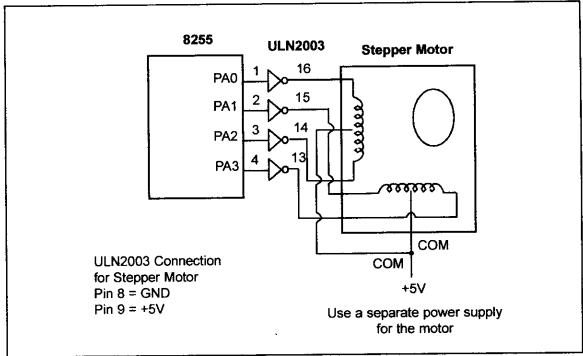

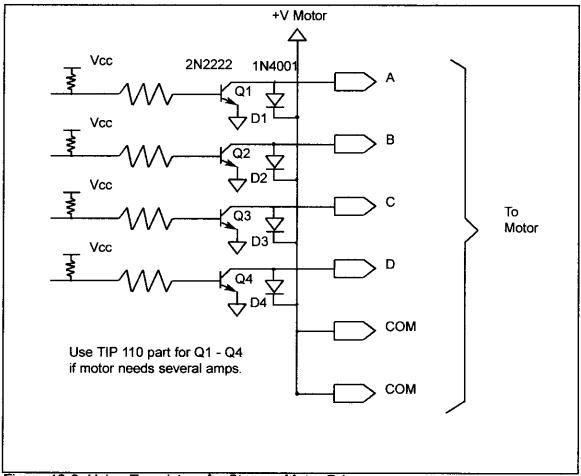

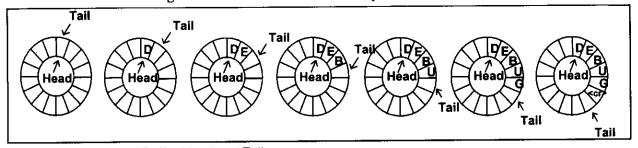

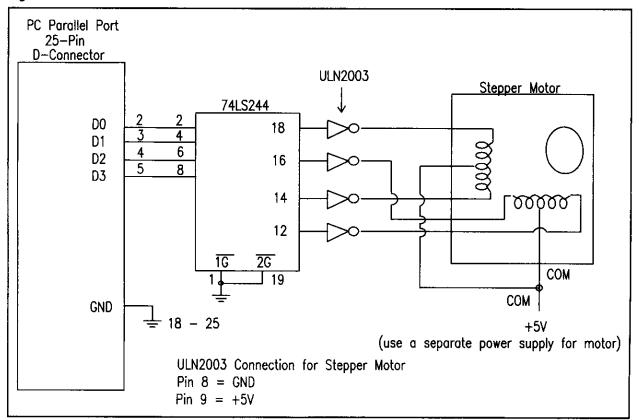

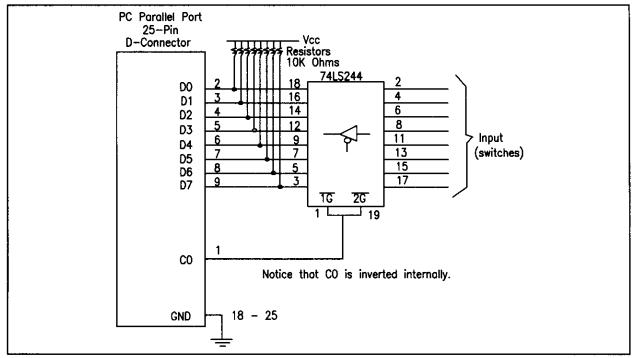

| SECTION 12.2: INTERFACING A STEPPER MOTOR TO A PC 362 Stepper motors 362 Step angle 363 Stepper motor connection and programming 364 Steps per second and RPM relation 365 The four-step sequence and number of teeth on rotor 365 Motor speed 366 Holding torque 366 Wave drive 4-step sequence 367                                                                                            |

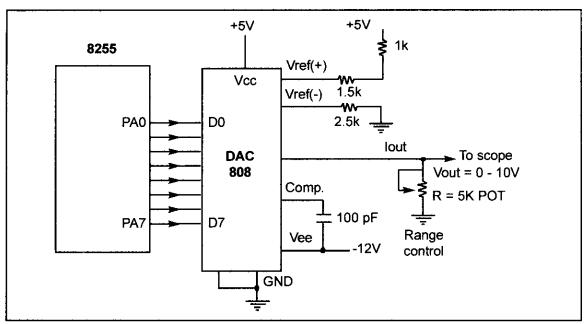

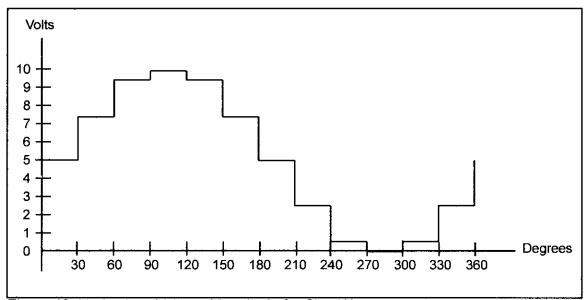

| SECTION 12.3: INTERFACING DAC TO A PC Digital-to-analog (DAC) converter 368 MC1408 DAC (or DAC 808) 369 Converting IOUT to voltage in 1408 DAC Generating a sine wave 369                                                                                                                                                                                                                       |

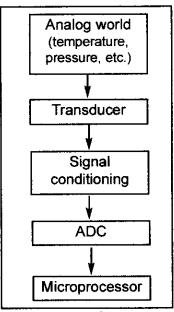

SECTION 12.4: INTERFACING ADC AND SENSORS TO THE PC 373

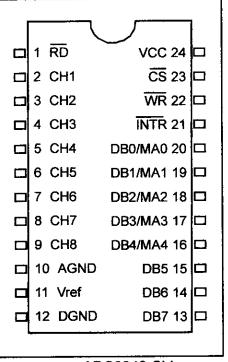

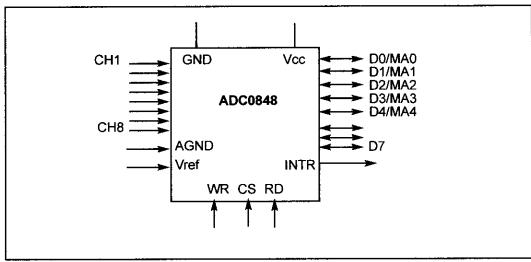

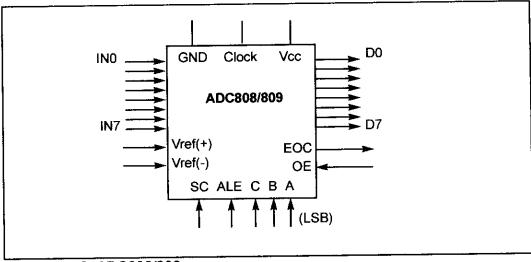

ADC devices 373

ADC 804 chip 373

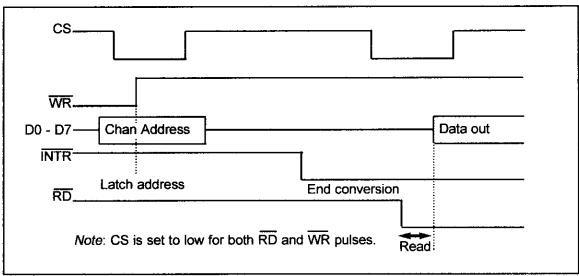

Selecting an input channel 376

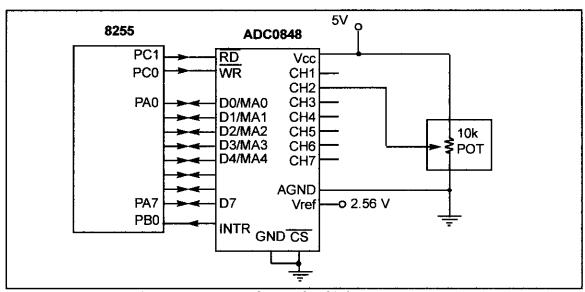

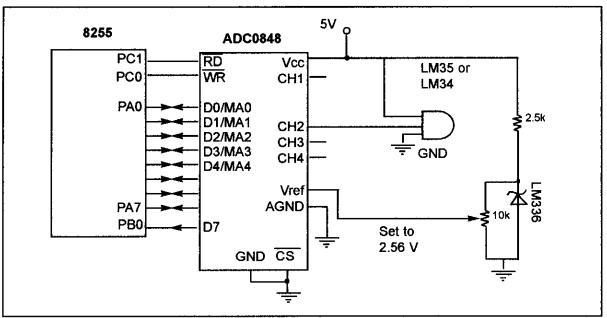

ADC0848 connection to 8255 377

Interfacing a temperature sensor to a PC 378

LM34 and LM35 temperature sensors 378

Signal conditioning and interfacing the LM35 to a PC 379

## CHAPTER 13: 8253/54 TIMER AND MUSIC 386

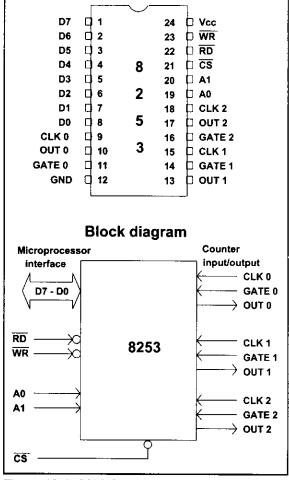

## SECTION 13.1: 8253/54 TIMER DESCRIPTION AND INITIALIZATION 387

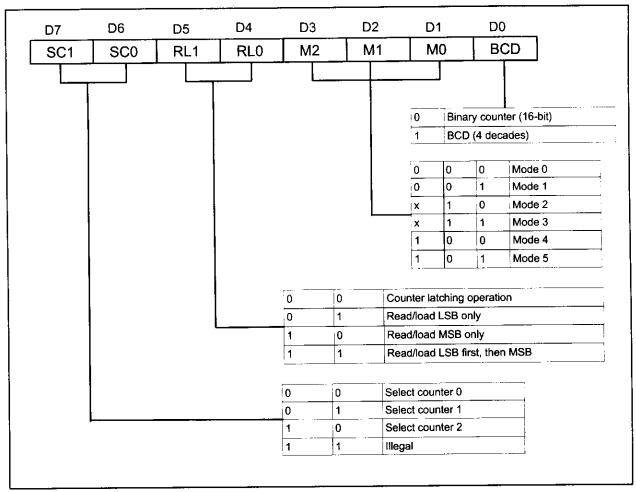

Initialization of the 8253/54 388

Control word 388

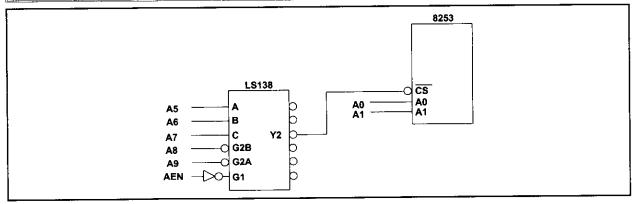

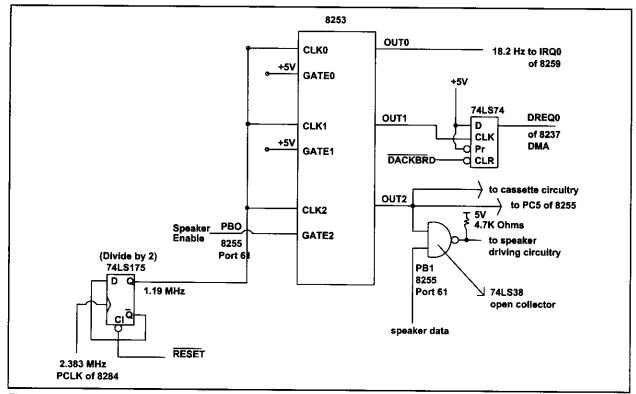

# SECTION 13.2: IBM PC 8253/54 TIMER CONNECTIONS AND PROGRAMMING 391

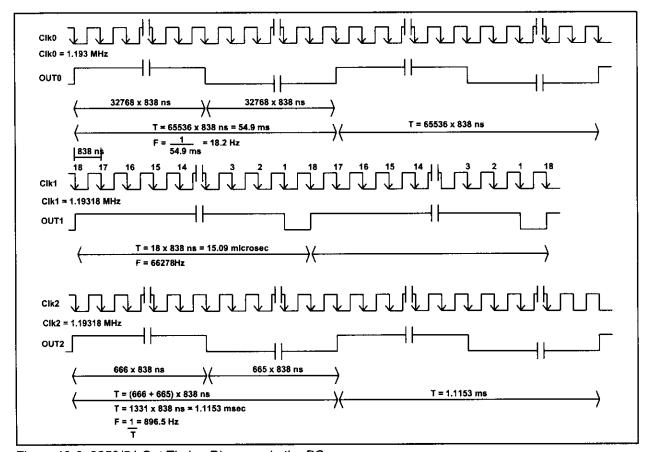

Using counter 0 392

Using counter 1 393

Using counter 2 393

Use of timer 2 by the speaker 394

Turning on the speaker via PB0 and PB1 of port 61H 394

Time delay for 80x86 PCs 394

Creating time delays in 8088/86-based computers 395

Time delays in 80x86 IBM PC for 286 and higher processors 395

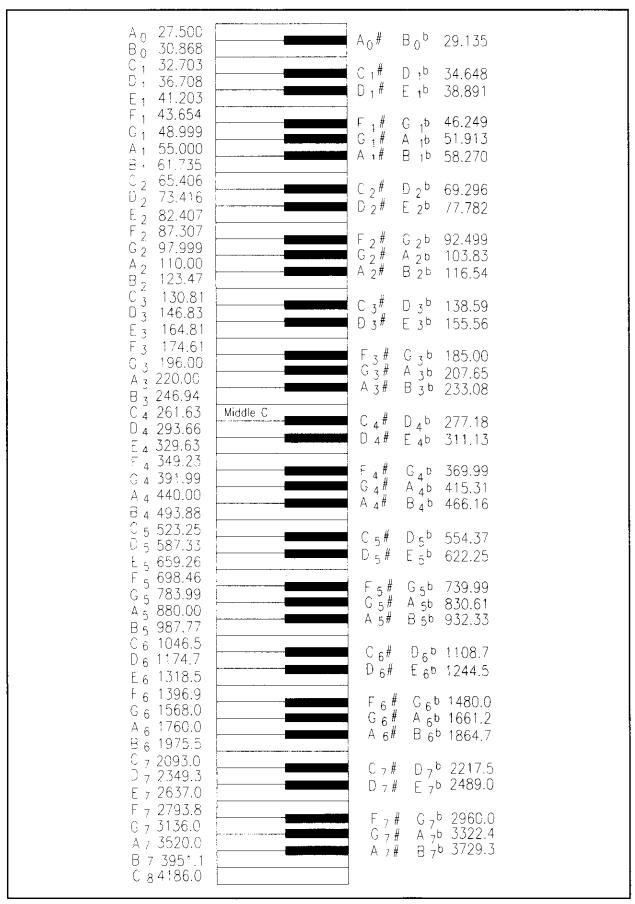

## SECTION 13.3: GENERATING MUSIC ON THE IBM PC 397 Playing "Happy Birthday" on the PC 399

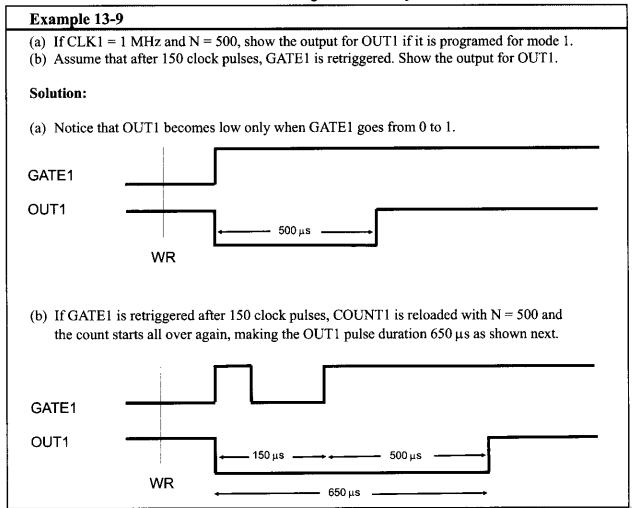

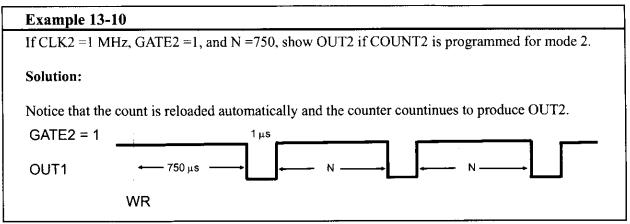

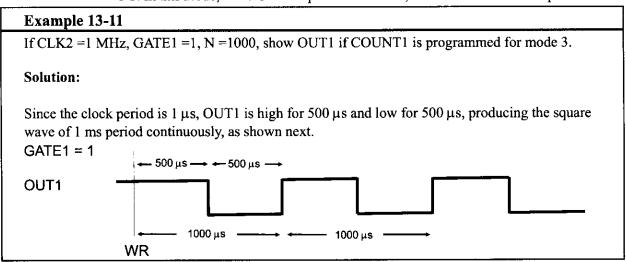

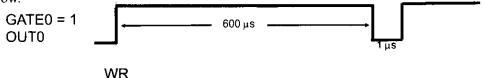

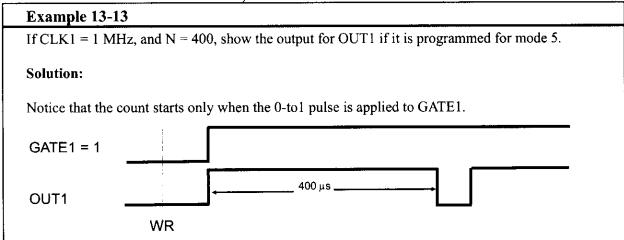

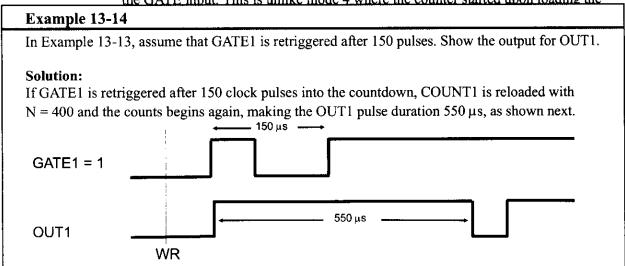

## SECTION 13.4: SHAPE of 8253/54 OUTPUTS 401

OUT0 pulse shape in IBM BIOS 401

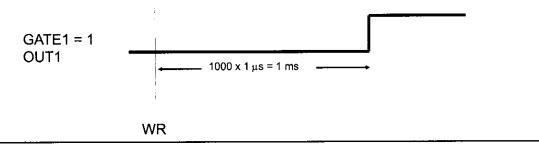

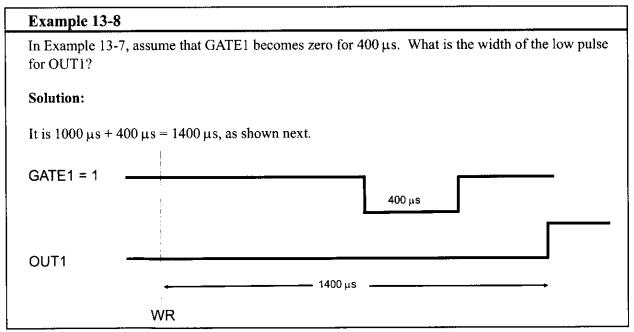

OUT1 pulse shape in IBM BIOS 402

OUT2 pulse shape in IBM BIOS 402

8253/54 modes of operation 402

Testing the 8255/54 timer of the PC Interface Trainer 407

## CHAPTER 14: INTERRUPTS AND THE 8259 CHIP 410

## SECTION 14.1: 8088/86 INTERRUPTS 411

Interrupt service routine (ISR) 411

Difference between INT and CALL instructions 412

Categories of interrupts 413

Hardware interrupts 413

Software interrupts 413

Interrupts and the flag register 414

Processing interrupts 414

Functions associated with INT 00 to INT 04 415

| SECTION 14.2: IBM PC AND DOS ASSIGNMENT OF INTERRUPTS | 417 |

|-------------------------------------------------------|-----|

| Examining the interrupt vector table of your PC 417   |     |

| Analyzing an IBM BIOS interrupt service routine 419   |     |

| INT 12H: checking the size of RAM on the IBM PC 4     | 19  |

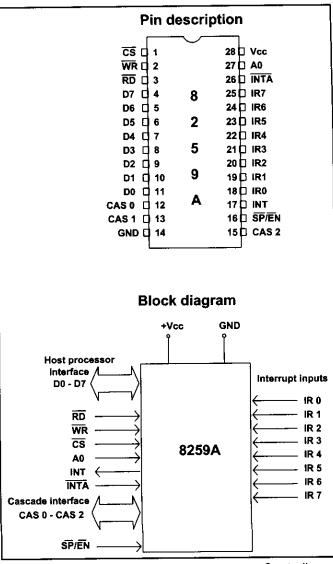

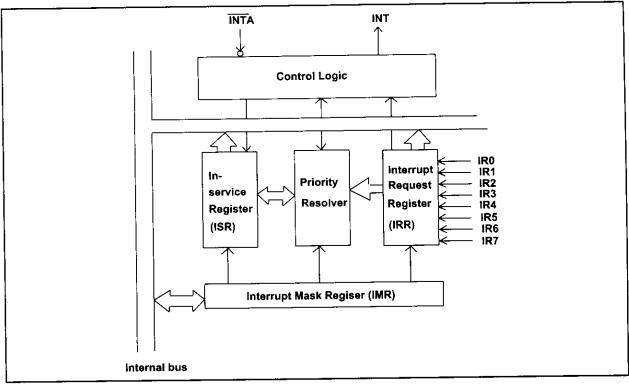

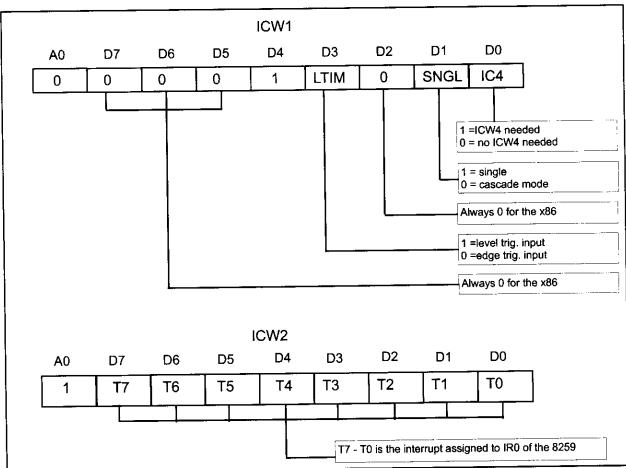

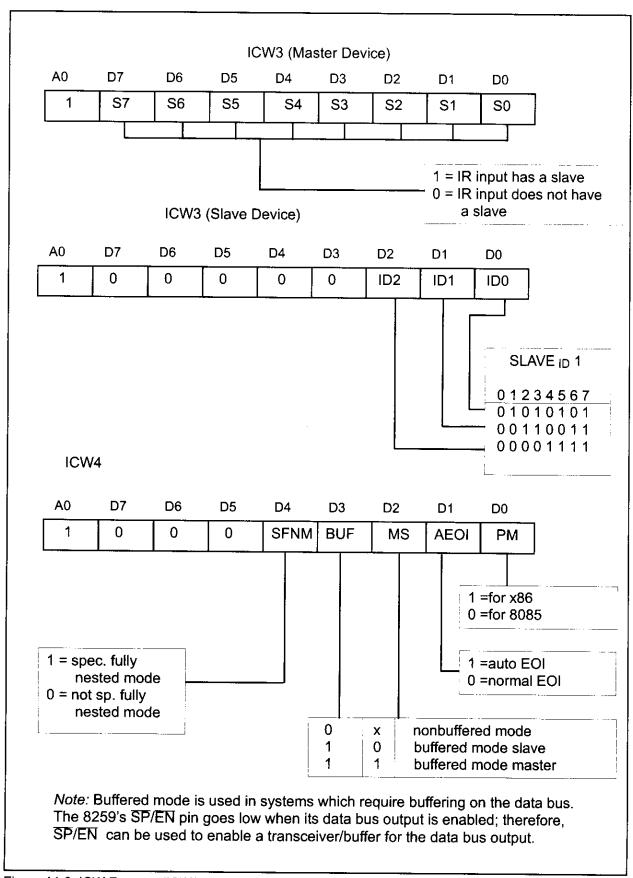

## SECTION 143: 8259 PROGRAMMABLE INTERRUPT CONTROLLER 420 8259 control words and ports 421 Masking and prioritization of IR0 - IR7 interrupts 426

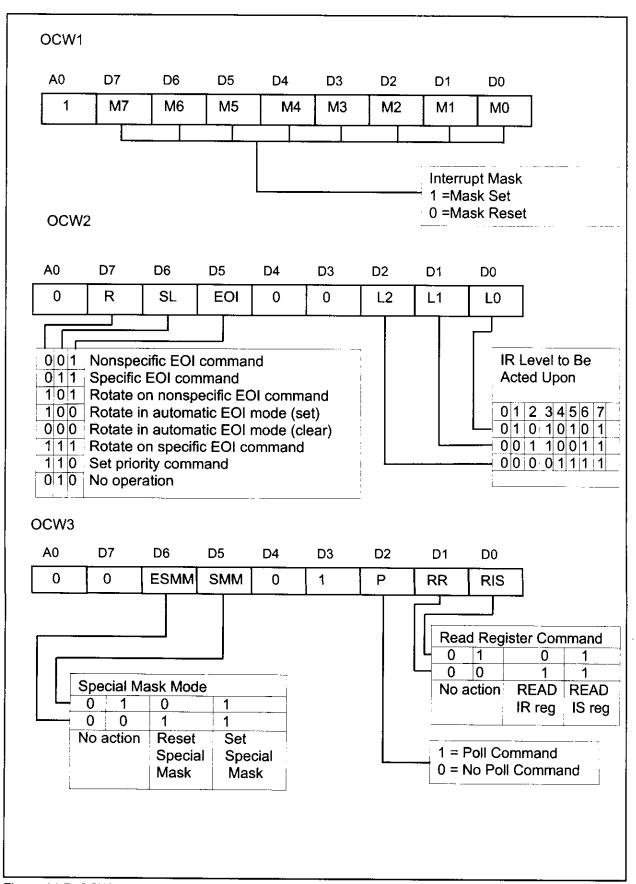

OCW (operation command word) 426 427

OCW1 (operation command word 1)

OCW2 (operation command word 2) 427

Importance of the EOI (end of interrupt) command 429 OCW3 (operation command word 3) 429

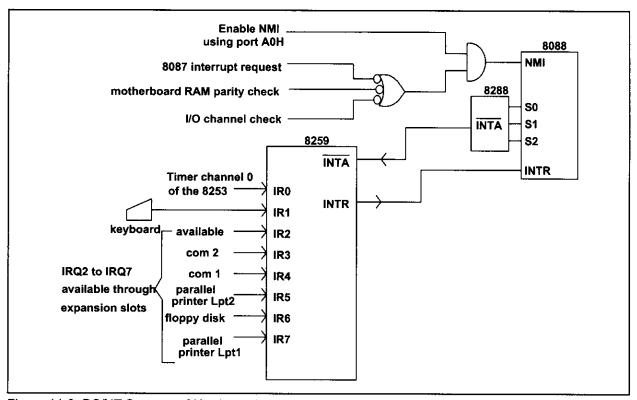

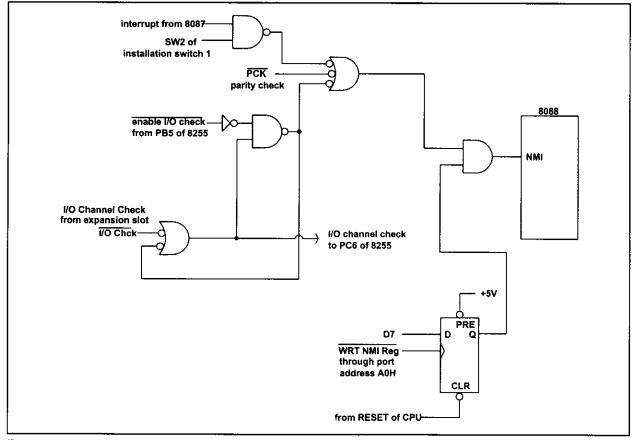

## SECTION 14.4: USE OF THE 8259 CHIP IN THE IBM PC/XT 430 Interfacing the 8259 to the 8088 in IBM PC/XT computers 430 Initialization words of the 8259 in the IBM PC/XT 431 Sequences of hardware interrupts with the 8259 Sources of hardware interrupts in the IBM PC/XT 433 Sources of NMI in the IBM PC 433

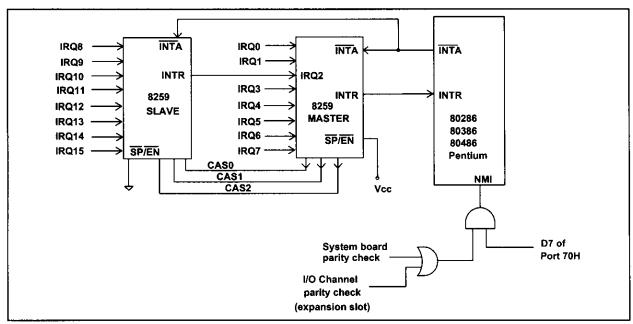

## SECTION 14.5: INTERRUPTS ON 80286 AND HIGHER 80x86 PCs 436 IBM PC AT hardware interrupts 436 8259 in master mode 436 8259 in slave mode 437 AT-type computers interrupt assignment 438 Case of missing IROs on the AT expansion slot 80x86 microprocessor generated interrupts (exceptions) 439 Interrupt priority 441 More about edge- and level-triggered interrupts 441

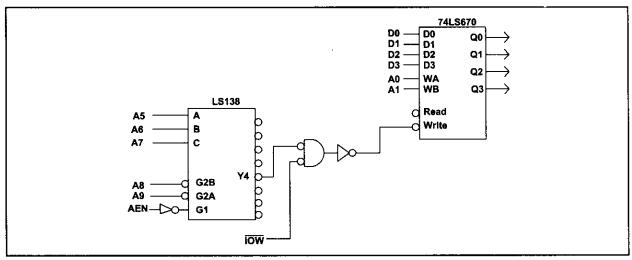

## CHAPTER 15: DIRECT MEMORY ACCESSING; THE 8237 DMA CHIP 447

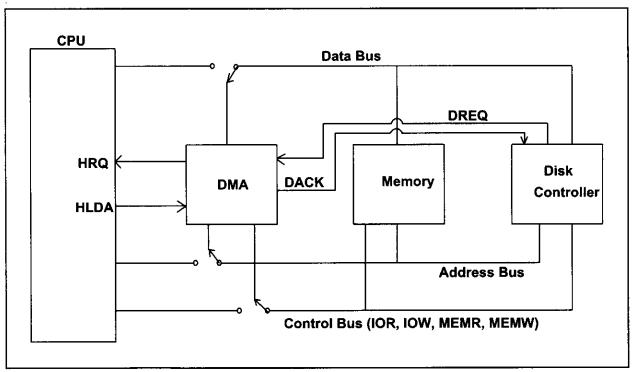

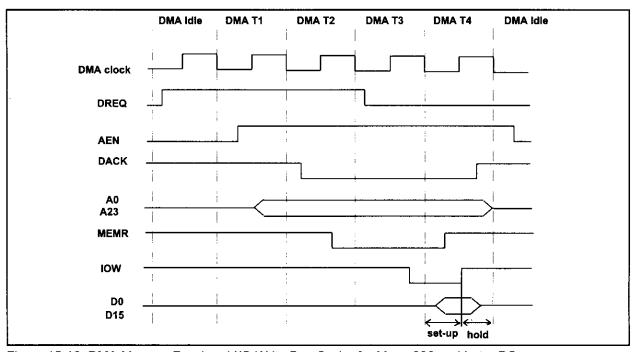

#### SECTION 15.1: CONCEPT OF DMA 448

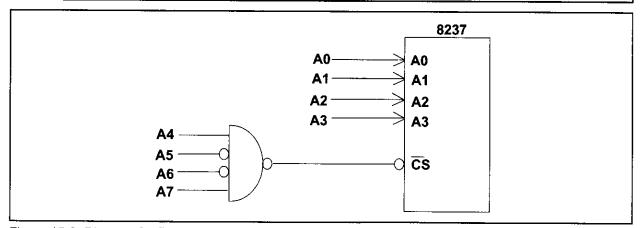

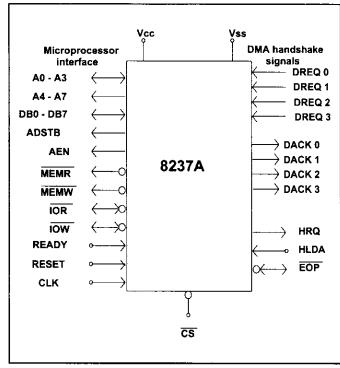

### SECTION 15.2: 8237 DMA CHIP PROGRAMMING 450

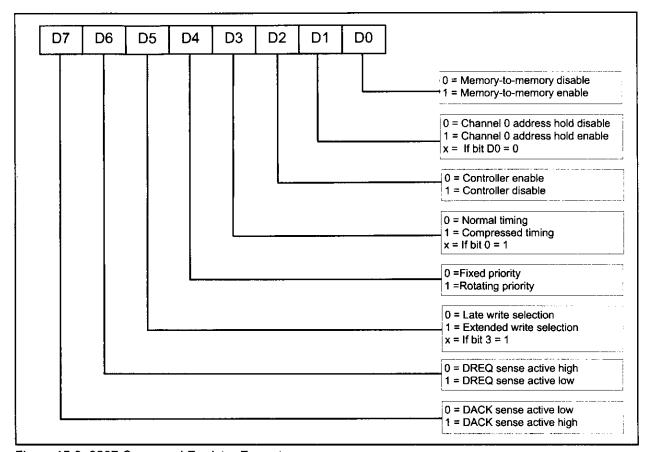

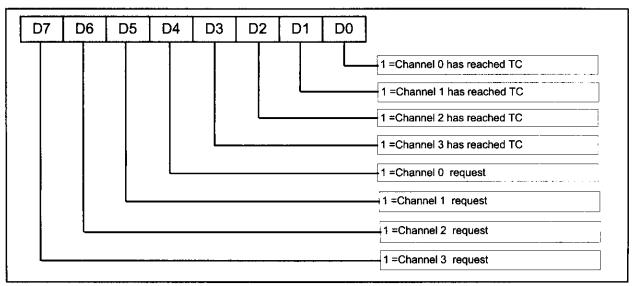

8237's internal control registers 453

Interrupt sharing in the x86 PC 442

Command register 453

Status register 454

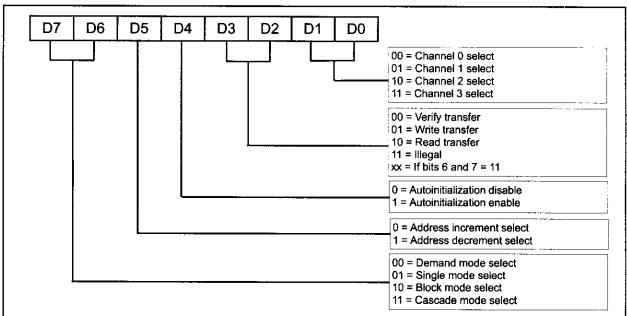

Mode register 456

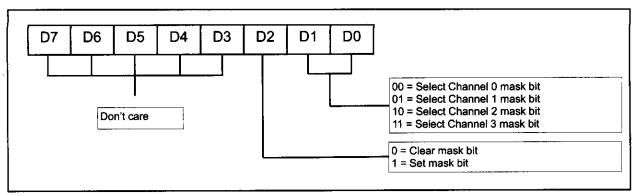

Single mask register 457

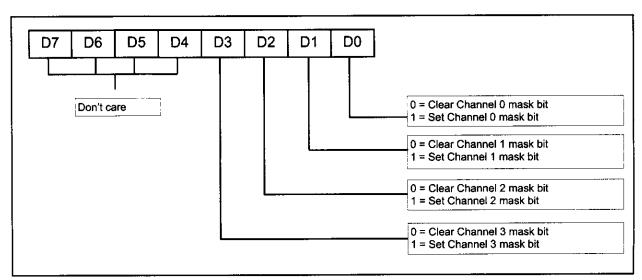

All mask register 457

Master clear/temporary register 458

Clear mask register 459

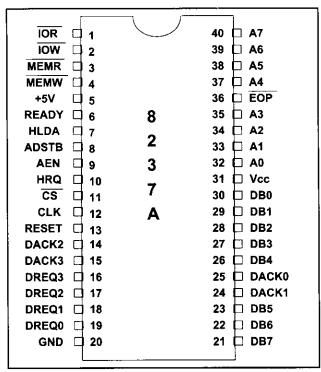

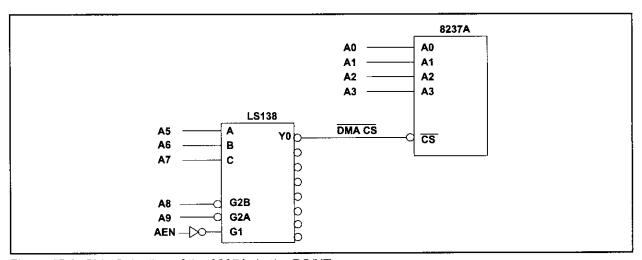

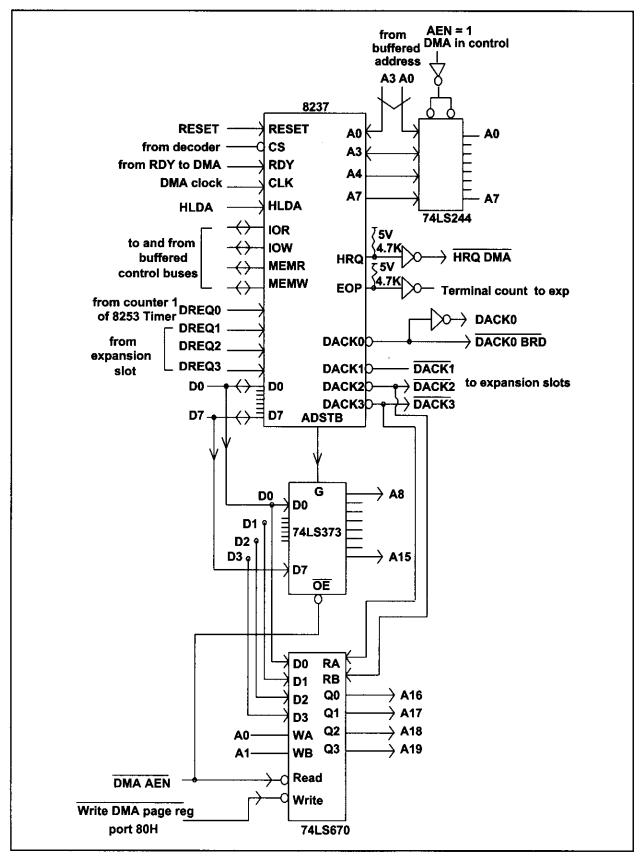

## SECTION 15.3: 8237 DMA INTERFACING IN THE IBM PC/XT 459 8237 and 8088 connections in the IBM PC 459 Channel assignment of the 8237 in the IBM PC/XT 463 DMA page register 463 DMA data transfer rate of the PC/XT 464

## SECTION 15.4: REFRESHING DRAM USING CHANNEL 0 OF THE 8237 465

Refreshing DRAM with the 8237 467

Refreshing in the IBM PC/XT 467

DMA cycle of channel 0 467

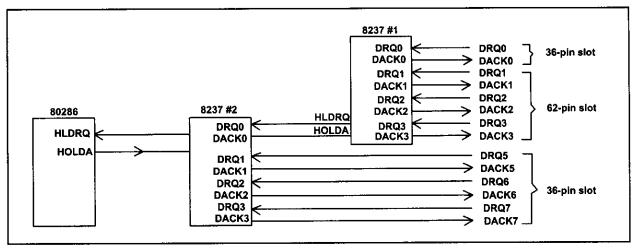

## SECTION 15.5: DMA IN 80x86-BASED PC AT-TYPE COMPUTERS 468

8237 DMA #1 468

469 8237 DMA #2

Points to be noted regarding 16-bit DMA channels 470

DMA channel priority 471

I/O cycle recovery time 471

DMA transfer rate 472

## CHAPTER 16: VIDEO AND VIDEO ADAPTERS 477

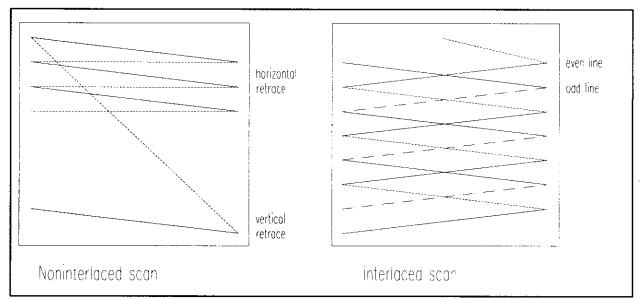

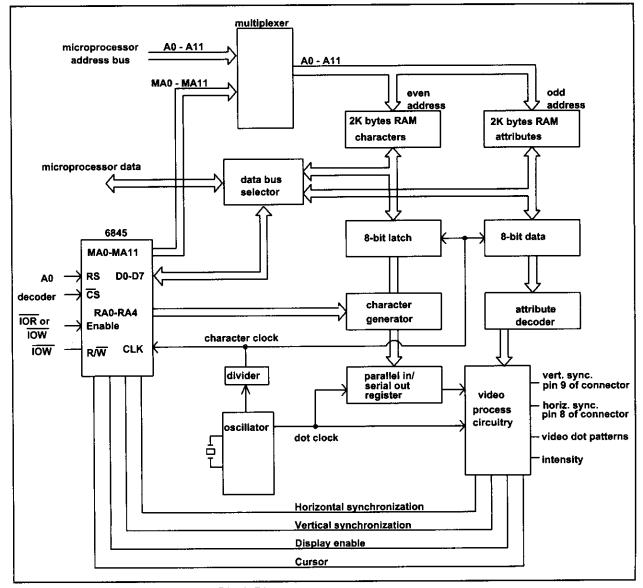

## SECTION 16.1: PRINCIPLES OF MONITORS AND VIDEO ADAPTERS 478

How to judge a monitor 478

Dot pitch

480 Dot pitch and monitor size 480

Phosphorous materials

Color monitors 481

Analog and digital monitors 481

Video display RAM and video controller 481

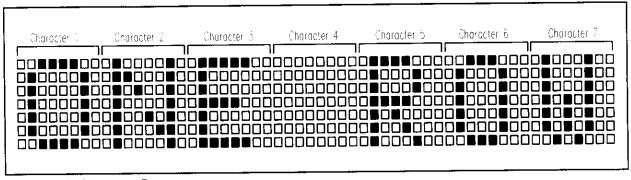

Character box 482

## SECTION 16.2: VIDEO ADAPTERS AND TEXT MODE **PROGRAMMING 484**

CGA (color graphics adapter) 484

Video RAM in CGA 484

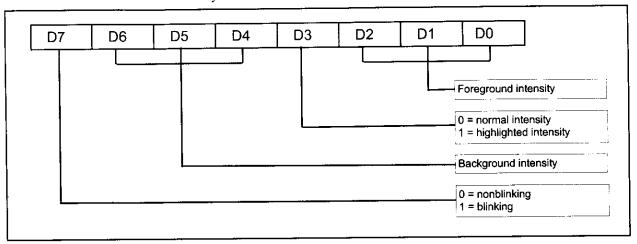

Attribute byte in CGA text mode 485

MDA (monochrome display adapter) 486

Video RAM in MDA 486

Attribute byte in IBM MDA 487

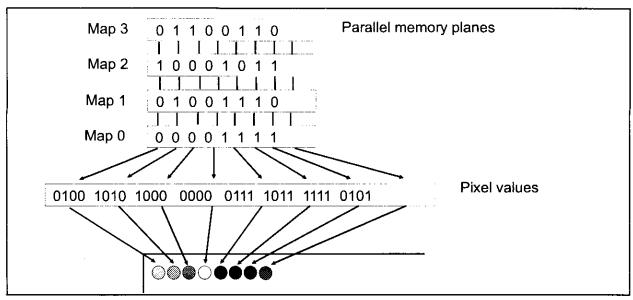

EGA (enhanced graphics adapter)

EGA video memory and attribute 487

MCGA (multicolor graphics array) 488

VGA (video graphics array)

Video memory and attributes in VGA

#### Super VGA (SVGA) and other video adapters 491

## SECTION 16.3: TEXT MODE PROGRAMMING USING INT 10H 491

489

Finding the current video mode 491

Changing the video mode 491

Setting the cursor position (AH=02) 493

Getting the current cursor position (AH=03) 493

Scrolling the window up to clear the screen (AH=06) 493

| Writing a character in teletype mode (AH=0E) 494 |

|--------------------------------------------------|

| Writing a string in teletype mode (AH=13H) 495   |

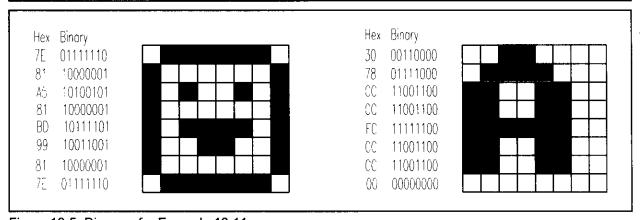

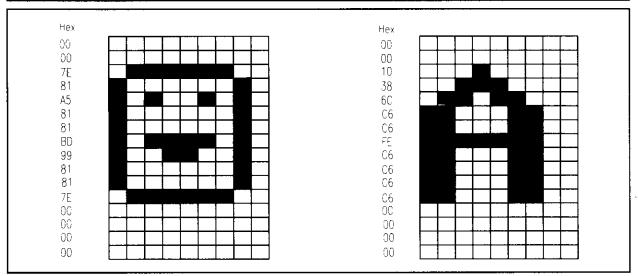

| Character generator ROM 495                      |

| How characters are displayed in text mode 497    |

| Character definition table in VGA 498            |

| Changing the cursor shape using INT 10H 498      |